microprocessors Motorola developed jointly with IBM as part of the AIM alliance, but remained available until the mid-1990s. Externally the 88110 has a von...

4 KB (484 words) - 20:28, 16 May 2024

superpipelined "Q", borrowing from the 88110 and anticipated as the 68060. Subsequent reports indicated that Motorola had considered the 68050 as not meriting...

43 KB (4,135 words) - 00:21, 22 December 2024

88000 (m88k for short) is a RISC instruction set architecture developed by Motorola during the 1980s. The MC88100 arrived on the market in 1988, some two years...

22 KB (2,722 words) - 15:42, 15 January 2025

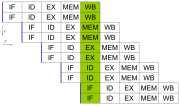

transistor counts, saw proliferation down to personal computers. The Motorola 88110 (1992) used a history buffer to revert instructions. Loads could be...

36 KB (4,220 words) - 00:00, 3 January 2025

|journal= ignored (help) Diefendorff, K.; Allen, M. (Spring 1992). "The Motorola 88110 Superscalar RISC microprocessor". Digest of Papers COMPCON Spring 1992...

13 KB (1,634 words) - 08:29, 3 January 2025

willing to license it to third parties. In mid-1990, Apple chose the Motorola 88110, an as-yet unfinished chip that combined the 88100 CPU and 88200 FPU...

50 KB (5,857 words) - 19:18, 10 December 2024

Motorola Single Board Computers is Motorola's production line of computer boards for embedded systems. There are three different lines : mvme68k, mvmeppc...

4 KB (211 words) - 10:57, 13 January 2024

PowerPC 600 (category Motorola microprocessors)

incorporate the 88110 bus architecture to the 601 for the benefit of the alliance and its customers, Motorola management provided not only the 88110 bus architecture...

35 KB (4,360 words) - 13:05, 21 January 2025

based on the Motorola 88110 processor, but it was later redesigned around dual PowerPC 601s, due to a lack of confidence in Motorola's commitment to...

60 KB (5,838 words) - 06:25, 7 January 2025

used for graphics processing. The graphics card contained a pair of Motorola 88110 RISC processors, 8 MB of DRAM and 4 MB of VRAM. The graphics processors...

28 KB (2,878 words) - 23:20, 13 November 2024

joined Motorola and was the chief architect of a second-generation implementation of the 88000 instruction set architecture, the 88110. The 88110 was not...

3 KB (277 words) - 10:53, 8 October 2024

Motorola 68851 (MMU) Motorola 68881 (FPU) Motorola 68882 (FPU) Motorola 68040 (w/FPU) Motorola 68060 (w/FPU) Motorola 88100 Motorola 88110 PPC 601 ("G1") PPC...

10 KB (998 words) - 01:50, 24 June 2024

Triton SCI system" early in 1992, combining elements of Orion with the Motorola 88110, awaiting SCI's ratification by the IEEE before committing to a final...

16 KB (1,700 words) - 05:24, 1 August 2024

January 1994). "Microprocessor Report's Annual Chip Awards Declare Motorola 88110 the Part least likely to...". Computer Business Review. Computergram...

29 KB (4,097 words) - 00:44, 2 January 2025

with the Infinity 90/ES in 1994. The ES supported between 2 and 2,045 Motorola 88110 CPUs running at 50 MHz. Several newer machines in the Infinity 90 series...

8 KB (842 words) - 05:01, 16 October 2024

In the early 1990s it was further upgraded to use the Motorola 88100 and 88110 Reduced Instruction Set Computing (RISC) CPUs. This RISC version of the...

16 KB (2,238 words) - 23:39, 25 April 2024