The instruction cycle (also known as the fetch–decode–execute cycle, or simply the fetch–execute cycle) is the cycle that the central processing unit (CPU)...

9 KB (1,182 words) - 03:11, 18 October 2024

instructions per cycle (IPC), commonly called instructions per clock, is one aspect of a processor's performance: the average number of instructions executed...

5 KB (596 words) - 04:19, 15 April 2024

In computer architecture, cycles per instruction (aka clock cycles per instruction, clocks per instruction, or CPI) is one aspect of a processor's performance:...

6 KB (914 words) - 16:41, 2 October 2024

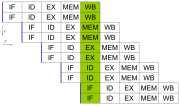

one stage for each step of the von Neumann cycle: Fetch the instruction, fetch the operands, do the instruction, write the results. A pipelined computer...

21 KB (2,571 words) - 01:33, 10 July 2024

flower parts may be arranged Menstrual cycle Cycles, a render engine for the software Blender Instruction cycle, the time period during which a computer...

5 KB (580 words) - 19:10, 20 November 2024

Program counter (redirect from Instruction pointer)

sections. Branch prediction Instruction cache Instruction cycle Instruction unit Instruction pipeline Instruction register Instruction scheduling Program status...

12 KB (1,382 words) - 06:42, 13 September 2024

Execution (computing) (section Instruction cycle)

"fetch–decode–execute" cycle for each instruction done by the control unit. As the executing machine follows the instructions, specific effects are produced...

15 KB (1,625 words) - 22:35, 10 October 2024

elements involved in executing the instruction. In the instruction cycle, the instruction is loaded into the instruction register after the processor fetches...

2 KB (239 words) - 08:51, 12 February 2024

instruction cycle is very rigid, and runs exactly as specified by the programmer. In the instruction fetch part of the cycle, the value of the instruction pointer...

3 KB (324 words) - 22:38, 5 April 2024

ARM architecture family (redirect from Arm instruction set)

register-register move) instructions, so that, for example, the statement in C language: a += (j << 2); could be rendered as a one-word, one-cycle instruction: ADD Ra...

141 KB (13,701 words) - 23:11, 16 November 2024

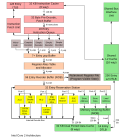

Microarchitecture (category Instruction processing)

the control logic, the combination of cycle counter, cycle state (high or low) and the bits of the instruction decode register determine exactly what...

27 KB (3,571 words) - 01:08, 17 May 2024

In computer science, an instruction set architecture (ISA) is an abstract model that generally defines how software controls the CPU in a computer or...

35 KB (4,286 words) - 21:15, 9 November 2024

Central processing unit (redirect from Instruction decoder)

collectively known as the instruction cycle. After the execution of an instruction, the entire process repeats, with the next instruction cycle normally fetching...

100 KB (11,315 words) - 10:36, 20 November 2024

some high-performance CISC "supercomputers" in order to reduce the instruction cycle time (despite the complications of implementing within the limited...

15 KB (1,980 words) - 13:28, 15 November 2024

clock cycle, a superscalar processor can execute more than one instruction during a clock cycle by simultaneously dispatching multiple instructions to different...

13 KB (1,621 words) - 23:14, 12 November 2024

instruction cycle successively. This consists of fetching the instruction, fetching the operands, decoding the instruction, executing the instruction...

30 KB (4,299 words) - 13:39, 13 July 2024

Classic RISC pipeline (category Instruction processing)

instruction fetch has a latency of one clock cycle (if using single-cycle SRAM or if the instruction was in the cache). Thus, during the Instruction Fetch...

24 KB (3,613 words) - 00:16, 14 November 2024

{\text{clock}}\times {\frac {\text{Is}}{\text{cycle}}}} However, the instructions/cycle measurement depends on the instruction sequence, the data and external factors...

64 KB (3,347 words) - 08:20, 8 September 2024

Out-of-order execution (redirect from Instruction dispatch)

processing units to make use of instruction cycles that would otherwise be wasted. In this paradigm, a processor executes instructions in an order governed by...

36 KB (4,280 words) - 18:35, 21 October 2024

A single cycle processor is a processor that carries out one instruction in a single clock cycle. Complex instruction set computer, a processor executing...

873 bytes (112 words) - 17:38, 5 January 2022

computer's instruction stream", thus seeking to deliver an average throughput approaching one instruction per cycle for any single instruction stream. Other...

58 KB (6,883 words) - 21:09, 10 November 2024

one branch. Each of them can issue one instruction per basic instruction cycle, but can have several instructions in process. These are what correspond...

2 KB (264 words) - 20:08, 20 November 2024

The x86 instruction set refers to the set of instructions that x86-compatible microprocessors support. The instructions are usually part of an executable...

254 KB (14,117 words) - 01:37, 17 November 2024

Digital signal processor (section Instruction sets)

accesses per instruction cycle – typically supporting reading 2 data values from 2 separate data buses and the next instruction (from the instruction cache,...

26 KB (2,924 words) - 22:34, 3 November 2024

PDP-10 (section Instruction set architecture)

already running, the system stops at the next memory read part of the instruction cycle and instead begins processing at the address stored in the first of...

50 KB (5,570 words) - 16:53, 22 September 2024

topic of: Multi Cycle Processors A multi-cycle processor is a processor that carries out one instruction over multiple clock cycles, often without starting...

2 KB (165 words) - 15:17, 10 October 2020

fetch and decode instructions, as well as load data operands from memory (as part of the instruction cycle), to execute the instructions constituting the...

20 KB (1,772 words) - 21:45, 24 October 2024

1971 release. Instruction cycle time: minimum 10.8 μs (8 clock cycles per machine cycle). Instruction execution time 1 or 2 machine cycles (10.8 or 21.6 μs)...

56 KB (6,724 words) - 20:55, 8 October 2024

PIC microcontrollers (section Instruction set)

instruction cycles. External interrupts have to be synchronized with the four-clock instruction cycle, otherwise there can be a one instruction cycle...

65 KB (8,051 words) - 18:05, 22 October 2024

Commons has media related to ARM Cortex-A7. ARM Holdings Official website Cortex-A7 Technical Reference Manuals Other Cortex-A7 instruction cycle timings...

9 KB (623 words) - 15:18, 29 September 2024