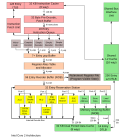

on. These processors are designed by Imagination Technologies, MIPS Technologies, and others. It displays an overview of the MIPS processors with performance...

15 KB (280 words) - 13:43, 1 February 2024

Since 1985, many processors implementing some version of the MIPS architecture have been designed and used widely. The first MIPS microprocessor, the R2000...

29 KB (3,604 words) - 15:57, 10 February 2023

2022, at the Wayback Machine, etc.) DLX List of MIPS architecture processors MIPS architecture processors Pipeline (computing) Prpl Foundation Patterson...

72 KB (8,204 words) - 04:23, 29 July 2024

This generational list of Intel processors attempts to present all of Intel's processors from the 4-bit 4004 (1971) to the present high-end offerings....

178 KB (13,535 words) - 20:28, 30 August 2024

Reduced instruction set computer (redirect from RISC architecture)

concepts in two seminal projects, Stanford MIPS and Berkeley RISC. These were commercialized in the 1980s as the MIPS and SPARC systems. IBM eventually produced...

58 KB (6,816 words) - 13:12, 25 August 2024

500 mips MIPS32 emulator, can be used to develop software using virtual platforms, emulators including MIPS processors running at up to 500 MIPS for MIPS32...

7 KB (778 words) - 06:12, 14 April 2024

originally Acorn RISC Machine) is a family of RISC instruction set architectures (ISAs) for computer processors. Arm Ltd. develops the ISAs and licenses...

139 KB (13,604 words) - 18:06, 6 September 2024

Loongson (category MIPS implementations)

The processors are alternately called Godson processors, which is described as its academic name. The Godson processors, based on MIPS architecture, were...

60 KB (4,535 words) - 22:35, 18 August 2024

an architectural license from ARM. The following table lists each core by the year it was announced. Electronics portal Comparison of ARM processors List...

62 KB (1,671 words) - 03:05, 22 August 2024

Instructions per second (redirect from Millions of instructions per second)

measured in thousand instructions per second (1000 kIPS = 1 MIPS). zMIPS refers to the MIPS measure used internally by IBM to rate its mainframe servers...

64 KB (3,330 words) - 10:31, 21 August 2024

Xilinx (microblaze) MIPS architecture (mips): Dingoo Infineon's Amazon & Danube Network Processors Ingenic Jz4740 Loongson (MIPS-compatible), and models...

14 KB (1,399 words) - 20:06, 21 July 2024

2010. MIPS64 Architecture for Programmers: Release 6 MIPS32 Architecture for Programmers: Release 6 MIPS Open "Wave Computing Closes Its MIPS Open Initiative...

33 KB (1,795 words) - 21:05, 28 May 2024

Status register (redirect from Processor flag)

memory. This is a list of the most common CPU status register flags, implemented in almost all modern processors. On some processors, the status register...

9 KB (804 words) - 02:24, 20 December 2022

larger register. Processors that have the ability to execute single instructions on multiple data are called vector processors. A processor often contains...

32 KB (1,529 words) - 03:23, 16 August 2024

MIPS32 microAptiv UC Core MIPS architecture PIC32MX series: 32-bit instructions, uses the MIPS32 M4K Core MIPS architecture PIC32MZ series: 32-bit instructions...

27 KB (2,522 words) - 16:28, 4 September 2024

Silicon Graphics (category CS1 maint: numeric names: authors list)

increased, MIPS' existing R10000-based machines grew increasingly uncompetitive. Eventually it was forced to introduce faster MIPS processors, the R12000...

71 KB (7,261 words) - 04:00, 5 September 2024

size. Even some CISC processors (based on architectures that were created before RISC grew dominant), such as newer x86 processors, translate instructions...

42 KB (5,617 words) - 03:47, 31 July 2024

SPARC (redirect from Scalable Processor ARChitecture)

1993, introduced a 64-bit architecture and was first released in Sun's UltraSPARC processors in 1995. Later, SPARC processors were used in symmetric multiprocessing...

74 KB (6,103 words) - 17:28, 18 July 2024

uses low-power processors with an ARM core; runs Linux, Android, and OpenWRT BeagleBoard, uses low-power Texas Instruments processors with an ARM Cortex-A8...

17 KB (1,621 words) - 09:58, 4 September 2024

of manufacturers utilize AMBA buses for non-ARM designs. As an example Infineon uses an AMBA bus for the ADM5120 SoC based on the MIPS architecture....

10 KB (1,311 words) - 21:55, 13 April 2024

I386 (section Architecture)

capable of 7 MIPS. A 33 MHz 80386 was reportedly measured to operate at about 11.4 and 11.5 MIPS. At that same speed, it has the performance of 8 VAX MIPS. These...

50 KB (4,943 words) - 15:13, 28 August 2024

Pentium (original) (redirect from Pentium compatible processor)

instructions per second (MIPS), and the 75 MHz model was able to reach 126.5 MIPS in certain benchmarks. The Pentium architecture typically offered just...

36 KB (3,491 words) - 04:41, 5 September 2024

the MIPS IV instruction set architecture (ISA), 350 MHz clock rate KOMDIV128-RIO – coprocessor NTC Module NeuroMatrix – digital signal processor (DSP)...

4 KB (373 words) - 19:26, 2 April 2024

October 2007. "ABI for the Arm Architecture". Developer.arm.com. Retrieved 4 February 2020. Eric Christopher (11 June 2003). "mips eabi documentation". binutils@sources...

9 KB (929 words) - 01:22, 19 February 2024

FLOPS (category Units of frequency)

As such, floating-point processors are ideally suited for computationally intensive applications. FLOPS and MIPS are units of measure for the numerical...

57 KB (3,343 words) - 18:59, 19 August 2024

SGI Visual Workstation (section Computer architecture)

series of workstation computers that are designed and manufactured by SGI. Unlike its other product lines, which used the 64-bit MIPS RISC architecture, the...

10 KB (1,233 words) - 18:26, 21 August 2024

John L. Hennessy (category MIPS Technologies)

began the MIPS project to investigate RISC processors, and in 1984, he used his sabbatical year to found MIPS Computer Systems Inc. to commercialize the...

24 KB (1,824 words) - 18:53, 6 September 2024

Microarchitecture (redirect from Micro-architecture)

than modern RISC processors (in several respects). However, the choice of instruction set architecture may greatly affect the complexity of implementing high-performance...

27 KB (3,571 words) - 01:08, 17 May 2024

Intel Atom (redirect from Low-Power Intel Architecture)

such as the Eee PC can deliver around 3300 MIPS and 2.1 GFLOPS in standard benchmarks, compared to 7400 MIPS and 3.9 GFLOPS for the similarly clocked (1...

41 KB (3,195 words) - 08:15, 5 August 2024

portable across all machines of the same architecture. Some popular processor architectures such as x86, 68000, and MIPS have seen many new capabilities...

7 KB (564 words) - 10:29, 5 May 2023