Wafer-scale integration (WSI) is a system of building very-large integrated circuit (commonly called a "chip") networks from an entire silicon wafer to...

10 KB (1,282 words) - 05:20, 31 July 2024

Integrated circuit (redirect from Small-scale integration)

stands for "ultra-large-scale integration" was proposed for chips of more than 1 million transistors. Wafer-scale integration (WSI) is a means of building...

87 KB (9,261 words) - 18:01, 15 October 2024

chip-scale package (CSP) technology, since the resulting package is practically of the same size as the die. Wafer-level packaging allows integration of...

6 KB (724 words) - 23:58, 25 October 2024

of integrating all components on a single-crystal silicon wafer, which led to small-scale integration (SSI) in the early 1960s, and then medium-scale integration...

15 KB (1,599 words) - 03:19, 10 October 2024

currently part of the Analog MEMS and Sensors business group; In 2000, WaferScale Integration Inc. (WSI, Fremont, California), a vendor of EPROM and flash memory-based...

38 KB (4,088 words) - 01:29, 20 October 2024

Ivor Catt (section Wafer scale integration)

College, Cambridge. Catt developed and patented some ideas on Wafer scale integration (WSI) in 1972, and published his work in Wireless World in 1981...

9 KB (997 words) - 20:46, 30 July 2024

Eclipse. On August 19, 2019, Cerebras announced its first-generation Wafer-Scale Engine (WSE).’ In November 2019, Cerebras closed its series E round with...

36 KB (3,629 words) - 18:30, 1 November 2024

technologies developed by the main company. These included Anamartic Ltd (wafer-scale integration), Shaye Communications Ltd (CT2 mobile telephony) and Cambridge...

30 KB (3,122 words) - 18:00, 22 October 2024

problem by producing all of the circuit boards on a single wafer, known as wafer scale integration (WSI). Instead of making many small boards and wiring them...

9 KB (1,134 words) - 04:06, 16 October 2024

since the communication requirements for the chips are the same. Wafer-scale integration is another possibility. The primary limitations on this method...

6 KB (684 words) - 01:53, 29 August 2024

Technologically these devices are all cryogenic and scaling to large numbers of qubits requires wafer-scale integration, a serious engineering challenge by itself...

115 KB (12,556 words) - 21:31, 24 October 2024

later went to work for a number of startups, including Synertek, Wafer Scale Integration and San Disk. He and Sanjay Mehrotra co-founded SanDisk in 1988...

3 KB (233 words) - 18:39, 15 July 2024

the design, modeling, and applications of multi-chip modules and wafer-scale integration. It was established in 1999 and ceased publication in 2010. The...

2 KB (98 words) - 03:54, 31 July 2024

technologies developed by the company. These included Anamartic Ltd. (wafer-scale integration) and Cambridge Computer Ltd. (Z88 portable computer and satellite...

45 KB (4,788 words) - 18:20, 24 October 2024

general, 3D integration is a broad term that includes such technologies as 3D wafer-level packaging (3DWLP); 2.5D and 3D interposer-based integration; 3D stacked...

81 KB (8,773 words) - 01:41, 24 October 2024

The idea of using an entire wafer for a single computer processor was in vogue at the time, see wafer scale integration. The worst-case scenario was...

54 KB (7,710 words) - 18:29, 13 August 2024

Embedded wafer level ball grid array (eWLB) is a packaging technology for integrated circuits. The package interconnects are applied on an artificial wafer made...

5 KB (656 words) - 16:32, 23 June 2024

multi-project wafer (MPW) semiconductor manufacturing arrangements allow customers to share tooling (like mask) and microelectronics wafer fabrication cost...

19 KB (2,004 words) - 21:39, 11 August 2024

a single wafer of electronic-grade silicon (EGS) or other semiconductor (such as GaAs) through processes such as photolithography. The wafer is cut (diced)...

5 KB (462 words) - 23:58, 25 October 2024

other three-dimensional integrated circuits Multi-chip module WSI (wafer-scale integration) Proximity communication Surface-mount components are usually smaller...

62 KB (3,396 words) - 21:48, 26 October 2024

The acronym WSI may refer to: Wafer-scale integration, a technique for building large integrated circuits Wall Street Institute, the former name of Wall...

2 KB (240 words) - 08:13, 28 March 2023

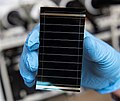

Perovskite solar cell (section Scalability)

sustainable technique for medium scale manufacturing, for instance, for standalone modules or Si wafer-scale integration. This work shows that through judicious...

185 KB (20,955 words) - 19:36, 6 September 2024

Semiconductor device fabrication (section Wafers)

of wafers from machine to machine. A wafer often has several integrated circuits which are called dies as they are pieces diced from a single wafer. Individual...

109 KB (11,548 words) - 07:14, 16 October 2024

Etching (microfabrication) (redirect from Wafer etching)

from the surface of a wafer during manufacturing. Etching is a critically important process module in fabrication, and every wafer undergoes many etching...

17 KB (1,558 words) - 09:49, 28 May 2024

vertical electrical connection (via) that passes completely through a silicon wafer or die. TSVs are high-performance interconnect techniques used as an alternative...

15 KB (1,733 words) - 14:36, 22 May 2024

18.7, p. 405. Rosenberg, Arnold L. (1986), "Book embeddings and wafer-scale integration", Proceedings of the seventeenth Southeastern international conference...

68 KB (8,167 words) - 00:16, 5 October 2024

they are still part of the wafer wafer-to-wafer (also wafer-on-wafer) stacking – bonding and integrating whole processed wafers atop one another before dicing...

14 KB (1,689 words) - 11:55, 18 October 2023

Very-large-scale integration (VLSI) lithography uses projection systems. Unlike contact or proximity masks, which cover an entire wafer, projection masks...

58 KB (6,445 words) - 02:12, 12 September 2024

semiconductor wafer. Process corners represent the extremes of these parameter variations within which a circuit that has been etched onto the wafer must function...

7 KB (923 words) - 17:12, 9 June 2024