The front-side bus (FSB) is a computer communication interface (bus) that was often used in Intel-chip-based computers during the 1990s and 2000s. The...

20 KB (1,827 words) - 10:57, 2 October 2024

back-side bus along with a front-side bus (FSB), the design is said to use a dual-bus architecture, or in Intel's terminology Dual Independent Bus (DIB)...

4 KB (404 words) - 15:33, 3 December 2023

which communicate by buses instead of networks, the system bus is known as a front-side bus. In such systems, the expansion bus may not share any architecture...

33 KB (4,239 words) - 03:49, 14 November 2024

Variants Pentium 955 EE – 3.46 GHz, 1066 MHz front-side bus Pentium 965 EE – 3.73 GHz, 1066 MHz front-side bus Nocona Introduced 2004 Irwindale Introduced...

178 KB (13,538 words) - 08:44, 14 November 2024

NetBurst (section Quad-Pumped Front-Side Bus)

the Core 2. The Northwood and Willamette cores feature an external Front Side Bus (FSB) that runs at 100 MHz which transfers four bits per clock cycle...

16 KB (1,648 words) - 12:59, 15 September 2024

available in large quantities later in 1997. These CPUs had a 66 MHz front-side bus and were initially used on motherboards equipped with the aging Intel...

23 KB (2,472 words) - 15:09, 21 October 2024

single local bus to the DIB, using the external front-side bus to the main system memory and I/O devices, and the internal back-side bus to the L2 CPU...

13 KB (1,638 words) - 07:44, 6 November 2024

Pentium III "Coppermine" core. The "Cascades" Xeon used a 133 MT/s front side bus and relatively small 256 kB on-die L2 cache resulting in almost the...

115 KB (7,794 words) - 15:15, 21 October 2024

The Runway bus is a front-side bus developed by Hewlett-Packard for use by its PA-RISC microprocessor family. The Runway bus is a 64-bit wide, split transaction...

3 KB (411 words) - 06:15, 15 July 2023

clock and was accessed via its own 64-bit back-side bus, allowing the processor to service both front-side bus requests and cache accesses simultaneously...

50 KB (5,116 words) - 01:52, 17 September 2024

HyperTransport (category Computer buses)

technology[clarification needed]—a wider range of RAM speeds on a common CPU bus than any Intel front-side bus. Intel technologies require each speed range of RAM to have...

21 KB (2,371 words) - 17:47, 2 November 2024

Intel Dynamic Front Side Bus Frequency Switching: Supported by E1, G0, G2, M0 Steppings Socket P processors can throttle the front-side bus (FSB) anywhere...

479 KB (14,082 words) - 05:11, 9 November 2024

original Duron was introduced with a 100 MHz (effectively 200 MHz) front-side bus – the same as the then current Socket A Athlons. Later with the introduction...

11 KB (1,220 words) - 18:39, 23 October 2024

run reliably at 450 MHz. This was achieved by simply increasing the front-side bus (FSB) clock rate from the stock 66 MHz to the 100 MHz clock of the Pentium...

54 KB (5,856 words) - 07:19, 16 October 2024

100 MHz front side bus, Pentium II CPUs were able to scale better in performance by reducing the difference between processor clock and bus speed. The...

7 KB (906 words) - 22:26, 24 May 2022

775. Whereas LGA 775 processors connect to a northbridge using the Front Side Bus, LGA 1156 processors integrate the features traditionally located on...

9 KB (600 words) - 00:13, 29 September 2024

Direct Media Interface (category Computer buses)

traffic and isochronous data transfer capabilities.: 3 DMI replaced FSB (Front Side Bus) which was elminated in 2009. DMI 1.0, introduced in 2004 with a data...

13 KB (1,222 words) - 04:09, 31 August 2024

III–branded CPU by adding the front-side bus (FSB) interface of Pentium 4, an improved instruction decoding and issuing front end, improved branch prediction...

16 KB (1,743 words) - 15:11, 21 October 2024

contains a "front side bus replacement block" that connects the CPU and GPU internally in exactly the same manner as the front side bus would have done...

11 KB (936 words) - 22:20, 9 October 2024

Slot A CPU interface used in some Athlon Thunderbird processors. The front-side bus frequencies supported for the AMD Athlon XP and Sempron are 133 MHz...

8 KB (736 words) - 11:32, 29 June 2024

CPU multiplier (redirect from Bus/core ratio)

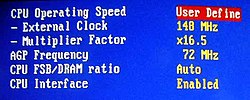

clock of 3.6 GHz. The external address and data buses of the CPU (often collectively termed front side bus (FSB) in PC contexts) also use the external clock...

7 KB (890 words) - 11:28, 19 August 2024

pinout 5 or 3.3 volts L1 Cache 32 kB (16 kB + 16 kB) 63 MHz on 25 MHz front side bus (25 × 2.5) PODP5V83 Introduced September 1995 234 pins, P24T pinout...

12 KB (1,475 words) - 18:50, 29 October 2024

Type can be Front side bus (FSB), HyperTransport (HT), Unified Media Interface (UMI), or PCI Express (PCIe). "Am386 SX/SXL/SXLV" (PDF). Advanced Micro...

51 KB (298 words) - 01:18, 14 January 2024

range is the last flagship range of Intel desktop processors to use a front-side bus (FSB). The introduction of Core 2 relegated the Pentium brand to the...

14 KB (856 words) - 00:10, 21 June 2024

33 MHz (33×3), and 50 MHz (50×2) front side bus 100 MHz capable edition for 33 MHz (33×3), and 25 MHz (25×4) front side bus 120/133 MHz capable edition for...

9 KB (984 words) - 23:46, 2 November 2024

the CPU, while adding certain features including a maximum 100 MHz front-side bus and support for AGP graphics cards. Super Socket 7 was used by AMD K6-2...

4 KB (359 words) - 17:38, 1 September 2024

memory hierarchy, e.g., last-level caches, front-side bus, memory socket connection.[citation needed] Bus contention Cache coherence Collision avoidance...

3 KB (293 words) - 15:42, 18 September 2024

transistors in 350 nm L1-Cache: 32 + 32 KB (data + instructions) MMX Socket 7 Front side bus: 66 MHz First release: April 2, 1997 VCore: 2.9 V (166/200) 3.2/3.3...

7 KB (676 words) - 05:26, 5 September 2024

but sometimes to allow for underclocking in order to maintain the front side bus speed (on older CPUs) compatibility with certain motherboards. Unlocking...

47 KB (5,885 words) - 00:25, 28 October 2024

older personal computers. It is connected directly to a CPU via the front-side bus (FSB), and is usually used in conjunction with a slower southbridge...

11 KB (1,289 words) - 00:24, 24 October 2024