Instructions per second (IPS) is a measure of a computer's processor speed. For complex instruction set computers (CISCs), different instructions take...

64 KB (3,347 words) - 08:20, 8 September 2024

the number of instructions by the number of CPU clock cycles. The number of instructions per second and floating point operations per second for a processor...

5 KB (596 words) - 04:19, 15 April 2024

For such cases, it is a more accurate measure than measuring instructions per second.[citation needed] Floating-point arithmetic is needed for very...

58 KB (3,341 words) - 13:36, 14 November 2024

per instruction for a program or program fragment. It is the multiplicative inverse of instructions per cycle. The average of Cycles Per Instruction in...

6 KB (914 words) - 16:41, 2 October 2024

per day (cpd) and cycles per year (cpy). Cycles per instruction (CPI) Cycles per metre Heinrich Hertz Instructions per cycle (IPC) Instructions per second...

5 KB (424 words) - 21:14, 1 February 2024

operations/second, then performance per watt can be written as operations/watt-second. Since a watt is one joule/second, then performance per watt can...

19 KB (2,000 words) - 18:33, 11 September 2024

Data-rate units (redirect from Kilobits per second)

terabits per second Binary prefix Bit rate List of interface bit rates Orders of magnitude (bit rate) Orders of magnitude (data) Metric prefix Instructions per...

17 KB (874 words) - 17:22, 17 November 2024

using less energy per instruction. Out of order CPUs can usually do more instructions per second because they can do several instructions at once. In a pipelined...

21 KB (2,571 words) - 01:33, 10 July 2024

commonly measured in floating-point operations per second (FLOPS) instead of million instructions per second (MIPS). Since 2022, supercomputers have existed...

81 KB (7,906 words) - 10:26, 20 November 2024

IBM 709 (section Instruction and data formats)

B instructions have, in sequence, a 12-bit instruction code (with the second and third bits set to 0 to distinguish them from type A instructions), a...

11 KB (1,042 words) - 06:41, 8 October 2024

based on a mix of instructions typical of scientific applications ("Gibson Mix") with the results in kilo Instructions Per Second (kIPS) per Longbottom, Roy...

82 KB (8,799 words) - 11:00, 11 November 2024

MCS-51 (section Instruction set)

8051 could thus execute 1 million one-cycle instructions per second or 500,000 two-cycle instructions per second. Enhanced 8051 cores are now commonly used...

58 KB (6,422 words) - 16:37, 25 October 2024

41 million instructions per second Dhrystone MIPS and SPEC integer rating of 27.9. It is approximately twice as fast as the i386 or i286 per clock cycle...

44 KB (4,073 words) - 01:00, 22 November 2024

Kenbak-1 (section Instruction table)

clock speed of 1 MHz), but the program speed averaged below 1,000 instructions per second due the many clock cycles needed for each operation and slow access...

14 KB (763 words) - 11:47, 22 November 2024

124 Whetstone instructions. Timing this program gave a measure of the machine's speed in thousands of Whetstone instructions per second (kWIPS). The Fortran...

20 KB (2,480 words) - 16:32, 2 November 2024

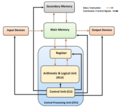

CPU cache (redirect from Second-level cache)

both executable instructions and data. A single TLB can be provided for access to both instructions and data, or a separate Instruction TLB (ITLB) and...

96 KB (13,298 words) - 19:32, 31 October 2024

individual instructions are written in simpler code. The goal is to offset the need to process more instructions by increasing the speed of each instruction, in...

58 KB (6,883 words) - 21:09, 10 November 2024

using less energy per instruction. Out-of-order CPUs can usually do more instructions per second because they can do several instructions at once. Control...

30 KB (4,299 words) - 13:39, 13 July 2024

so that they complete more instructions per clock cycle, thus achieving a lower CPI (cycles or clock cycles per instruction) count, although they may run...

13 KB (1,606 words) - 10:24, 21 November 2024

small instruction manual, which describes how the instructions are encoded. Also, it may define short (vaguely) mnemonic names for the instructions. The...

26 KB (3,176 words) - 05:34, 4 November 2024

sometimes measured in millions of instructions per second (MIPS), although the definition depends on the instruction mix measured. Examples of integer...

34 KB (3,748 words) - 11:13, 11 November 2024

Computer (redirect from Second-generation of computers)

"jump" instructions (or branches). Furthermore, jump instructions may be made to happen conditionally so that different sequences of instructions may be...

139 KB (14,027 words) - 22:53, 12 November 2024

intelligence, by estimating the computational cost (measured in instructions per second) of various operations of human intelligence, and comparing it...

14 KB (1,134 words) - 18:59, 28 October 2024

number of types of computer instructions so that it can operate at a higher speed (perform more millions of instructions per second, or MIPS). The Santa Clara...

4 KB (245 words) - 18:40, 4 March 2023

Linux kernel on comp.os.linux: [...] MIPS is short for Millions of Instructions Per Second. It is a measure for the computation speed of a processor. Like...

10 KB (1,008 words) - 05:29, 4 June 2024

contained 3,000 transistors and could execute approximately 62,000 instructions per second. General performance, bus layout and arithmetic logic unit (ALU)...

22 KB (2,256 words) - 08:02, 10 November 2024

Digital signal processor (section Data instructions)

many as 8000 MIPS (millions of instructions per second), use VLIW (very long instruction word), perform eight operations per clock-cycle and are compatible...

26 KB (2,924 words) - 22:34, 3 November 2024

approximately from 0.33 to 1 million instructions per second. Meanwhile, the mov reg,reg and ALU reg,reg instructions, taking two and three cycles respectively...

20 KB (2,547 words) - 00:52, 6 October 2024

This list compares various amounts of computing power in instructions per second organized by order of magnitude in FLOPS. Scientific E notation index:...

17 KB (1,660 words) - 15:47, 1 March 2024

IBM 650 (section Instruction set)

speed of the 650 was estimated to be around 27.6 ms per instruction, or roughly 40 instructions per second. Donald Knuth's series of books The Art of Computer...

38 KB (3,477 words) - 17:27, 28 August 2024