Intel 8259 – Wikipedia

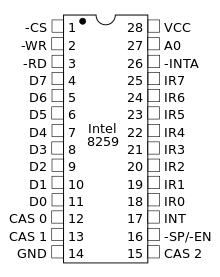

Der Intel 8259 ist ein programmierbarer Unterbrechungs-Steuerbaustein (Programmable Interrupt Controller, PIC), der primär für die Intel-8080/8085-Prozessoren entwickelt wurde. Später wurde der Chip auch zusammen mit dem Intel 8086/8088 und seinen Nachfolgern eingesetzt. Der Baustein wird hauptsächlich im 28-Pin-DIL-Gehäuse geliefert. Er wurde u. a. an NEC und Siemens lizenziert.

Er besitzt 8 Interrupt-Eingänge und einen Interrupt-Ausgang. Er wird seit den ersten PCs (IBM-PC XT) eingesetzt.[1] Die Eingänge sind dabei mit den Interrupt-Pins der Geräte im System verbunden (Tastatur, Timer, Drucker usw.), der Ausgang mit der CPU.

Verwendung

[Bearbeiten | Quelltext bearbeiten]Die 8 Eingänge reichten aufgrund der wachsenden Anzahl der Geräte im System schon bald nicht mehr aus, und es wurden stattdessen zwei Bausteine verwendet. Dabei wird der Ausgang des einen Bausteins (Slave) mit einem Eingang des anderen Bausteins (Master) verbunden (normalerweise am Eingang #2).[2] Die Funktionalität dieser beiden Bausteine ist längst nicht mehr in separaten Chips auf modernen Mainboards implementiert, sondern wird in den Chipsatz integriert.

Nachfolgende Skizze verdeutlicht die Kaskadierung und zeigt eine Beispielbelegung der Eingänge:

PIC 1 (Master) +--------------+ PIC 2 (Slave) | IRQ 0 + <--- Timer +-------------+ | IRQ 1 + <--- Tastatur | IRQ 8 + <--- Echtzeituhr | IRQ 2 +------------------+ | IRQ 9 + <--- ... | IRQ 3 + <--- Seriell | | IRQ 10 + <--- ... | IRQ 4 + <--- Seriell | | IRQ 11 + <--- ... | IRQ 5 + <--- Soundkarte | | IRQ 12 + <--- PS/2 Maus | IRQ 6 + <--- Floppy | | IRQ 13 + <--- Koprozessor | IRQ 7 + <--- Parallel | | IRQ 14 + <--- Festplatte +------+-------+ Port | | IRQ 15 + <--- Festplatte | | +-----+-------+ | | | | +--------------+ | +--->>> Zur CPU

Die meisten Eingänge sind dabei von der Architektur des PCs festgelegt und werden nicht von anderen Geräten verwendet, selbst wenn kein entsprechendes Gerät vorhanden ist.

Die Interrupts werden in einer bestimmten Reihenfolge abgearbeitet, die beim 8259 durch den Eingang festgelegt ist. Im Normalfall hat der Eingang 0 die höchste, der Eingang 7 die niedrigste Priorität. Damit ergibt sich folgende Reihenfolge: 0, 1, (2), 8, 9, 10, 11, 12, 13, 14, 15, 3, 4, 5, 6, 7. Die IRQ-Nummerierung wird dabei vom Mainboard vorgegeben: der 8259 addiert die Nummer des Eingangs zu einem konfigurierbaren Wert, und übergibt diesen dann der CPU. Die Nummerierung erfolgt aber üblicherweise wie in der Skizze angegeben.

Der IRQ 2 wird selbst nicht belegt, er ist die „Durchreiche“ für die IRQs des zweiten 8259 (sog. Kaskade, man spricht bei dieser Funktionsweise von Kaskadierung des 8259).

Die begrenzte Anzahl der Eingänge, die unflexible und langsame Programmierung und vor allem die fehlende Mehrprozessorsystemunterstützung haben zur Entwicklung eines Nachfolgers, dem APIC-System, geführt. Obwohl der PIC in aktuellen Chipsätzen zwar aus Kompatibilitätsgründen noch neben dem APIC vorhanden ist, wird er von modernen Betriebssystemen nicht mehr verwendet.

Literatur und Datenblätter

[Bearbeiten | Quelltext bearbeiten]- Josef Koller: 16 Bit Microcomputer. 1. Auflage, Hofacker Verlag, München 1981, ISBN 3-921682-80-0, Kap. 4.2.1 „Interruptcontroller 8259A“, S. 191–201.

- Martin Ernst, Andreas Stiller: PC-Bausteine. Interrupts: Der lange Weg einer Anforderung bis zur Bedienung. In: c’t. Heft 8, 1988, S. 174–187.

- Mikrocomputer Bausteine, Datenbuch 1979/80. Band 3, Peripherie, Siemens AG, Bestellnummer B 2049, S. 193–229.

- NEC Electronics (Europe) GmbH, 1982 Catalog, S. 675–692.

- Intel-Datenblatt: 8259A Programmable Interrupt Controller (8259A/8259A-2). (bochs.sourceforge.net GZIP; 257 kB).

Einzelnachweise

[Bearbeiten | Quelltext bearbeiten]- ↑ Technische Universität Chemnitz: Der Aufbau des Original-IBM-PC-Motherboards ( des vom 8. Dezember 2011 im Internet Archive) Info: Der Archivlink wurde automatisch eingesetzt und noch nicht geprüft. Bitte prüfe Original- und Archivlink gemäß Anleitung und entferne dann diesen Hinweis..

- ↑ Technische Universität Chemnitz: Das Motherboard des AT ( des vom 6. Januar 2012 im Internet Archive) Info: Der Archivlink wurde automatisch eingesetzt und noch nicht geprüft. Bitte prüfe Original- und Archivlink gemäß Anleitung und entferne dann diesen Hinweis..

French

French Deutsch

Deutsch