Semiconductor device fabrication

| Semiconductor device fabrication |

|---|

|

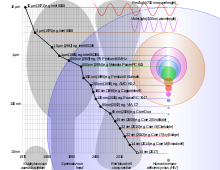

| MOSFET scaling (process nodes) |

Semiconductor device fabrication is the process used to manufacture semiconductor devices, typically integrated circuits (ICs) such as microprocessors, microcontrollers, and memories (such as RAM and flash memory). It is a multiple-step photolithographic and physico-chemical process (with steps such as thermal oxidation, thin-film deposition, ion-implantation, etching) during which electronic circuits are gradually created on a wafer, typically made of pure single-crystal semiconducting material. Silicon is almost always used, but various compound semiconductors are used for specialized applications.

The fabrication process is performed in highly specialized semiconductor fabrication plants, also called foundries or "fabs",[1] with the central part being the "clean room". In more advanced semiconductor devices, such as modern 14/10/7 nm nodes, fabrication can take up to 15 weeks, with 11–13 weeks being the industry average.[2] Production in advanced fabrication facilities is completely automated, with automated material handling systems taking care of the transport of wafers from machine to machine.[3]

A wafer often has several integrated circuits which are called dies as they are pieces diced from a single wafer. Individual dies are separated from a finished wafer in a process called die singulation, also called wafer dicing. The dies can then undergo further assembly and packaging.[4]

Within fabrication plants, the wafers are transported inside special sealed plastic boxes called FOUPs.[3] FOUPs in many fabs contain an internal nitrogen atmosphere[5][6] which helps prevent copper from oxidizing on the wafers. Copper is used in modern semiconductors for wiring.[7] The insides of the processing equipment and FOUPs is kept cleaner than the surrounding air in the cleanroom. This internal atmosphere is known as a mini-environment and helps improve yield which is the amount of working devices on a wafer. This mini environment is within an EFEM (equipment front end module)[8] which allows a machine to receive FOUPs, and introduces wafers from the FOUPs into the machine. Additionally many machines also handle wafers in clean nitrogen or vacuum environments to reduce contamination and improve process control.[3] Fabrication plants need large amounts of liquid nitrogen to maintain the atmosphere inside production machinery and FOUPs, which are constantly purged with nitrogen.[5][6] There can also be an air curtain or a mesh[9] between the FOUP and the EFEM which helps reduce the amount of humidity that enters the FOUP and improves yield.[10][11]

Companies that manufacture machines used in the industrial semiconductor fabrication process include ASML, Applied Materials, Tokyo Electron and Lam Research.

Feature size

[edit]

Feature size is determined by the width of the smallest lines that can be patterned in a semiconductor fabrication process, this measurement is known as the linewidth.[12][13] Patterning often refers to photolithography which allows a device design or pattern to be defined on the device during fabrication.[14] F2 is used as a measurement of area for different parts of a semiconductor device, based on the feature size of a semiconductor manufacturing process. Many semiconductor devices are designed in sections called cells, and each cell represents a small part of the device such as a memory cell to store data. Thus F2 is used to measure the area taken up by these cells or sections.[15]

A specific semiconductor process has specific rules on the minimum size (width or CD/Critical Dimension) and spacing for features on each layer of the chip.[16] Normally a new semiconductor process has smaller minimum sizes and tighter spacing. In some cases, this allows a simple die shrink of a currently produced chip design to reduce costs, improve performance,[16] and increase transistor density (number of transistors per unit area) without the expense of a new design.

Early semiconductor processes had arbitrary names for generations (viz., HMOS I/II/III/IV and CHMOS III/III-E/IV/V). Later each new generation process became known as a technology node[17] or process node,[18][19] designated by the process' minimum feature size in nanometers (or historically micrometers) of the process's transistor gate length, such as the "90 nm process". However, this has not been the case since 1994,[20] and the number of nanometers used to name process nodes (see the International Technology Roadmap for Semiconductors) has become more of a marketing term that has no standardized relation with functional feature sizes or with transistor density (number of transistors per unit area).[21]

Initially transistor gate length was smaller than that suggested by the process node name (e.g. 350 nm node); however this trend reversed in 2009.[20] Feature sizes can have no connection to the nanometers (nm) used in marketing. For example, Intel's former 10 nm process actually has features (the tips of FinFET fins) with a width of 7 nm, so the Intel 10 nm process is similar in transistor density to TSMC's 7 nm process. As another example, GlobalFoundries' 12 and 14 nm processes have similar feature sizes.[22][23][21]

History

[edit]20th century

[edit]

In 1955, Carl Frosch and Lincoln Derick, working at Bell Telephone Laboratories, accidentally grew a layer of silicon dioxide over the silicon wafer, for which they observed surface passivation effects.[25][26] By 1957 Frosch and Derick, using masking and predeposition, were able to manufacture silicon dioxide transistors; the first planar field effect transistors, in which drain and source were adjacent at the same surface.[27] At Bell Labs, the importance of their discoveries was immediately realized. Memos describing the results of their work circulated around Bell Labs before being formally published in 1957. At Shockley Semiconductor, Shockley had circulated the preprint of their article in December 1956 to all his senior staff, including Jean Hoerni,[28][29][30][31] who would later invent the planar process in 1959 while at Fairchild Semiconductor.[32][33]

In 1948, Bardeen patented an insulated-gate transistor (IGFET) with an inversion layer; Bardeen's concept forms the basis of MOSFET technology today.[34] An improved type of MOSFET technology, CMOS, was developed by Chih-Tang Sah and Frank Wanlass at Fairchild Semiconductor in 1963.[35][36] CMOS was commercialised by RCA in the late 1960s.[35] RCA commercially used CMOS for its 4000-series integrated circuits in 1968, starting with a 20 μm process before gradually scaling to a 10 μm process over the next several years.[37] Many early semiconductor device manufacturers developed and built their own equipment such as ion implanters.[38]

In 1963, Harold M. Manasevit was the first to document epitaxial growth of silicon on sapphire while working at the Autonetics division of North American Aviation (now Boeing). In 1964, he published his findings with colleague William Simpson in the Journal of Applied Physics.[39] In 1965, C.W. Mueller and P.H. Robinson fabricated a MOSFET (metal–oxide–semiconductor field-effect transistor) using the silicon-on-sapphire process at RCA Laboratories.[40]

Semiconductor device manufacturing has since spread from Texas and California in the 1960s to the rest of the world, including Asia, Europe, and the Middle East.

Wafer size has grown over time, from 25 mm (1 inch) in 1960, to 50 mm (2 inches) in 1969, 100 mm (4 inches) in 1976, 125 mm (5 inches) in 1981, 150 mm (6 inches) in 1983 and 200 mm in 1992.[41][42]

In the era of 2-inch wafers, these were handled manually using tweezers and held manually for the time required for a given process. Tweezers were replaced by vacuum wands as they generate fewer particles[43] which can contaminate the wafers. Wafer carriers or cassettes, which can hold several wafers at once, were developed to carry several wafers between process steps, but wafers had to be individually removed from the carrier, processed and returned to the carrier, so acid-resistant carriers were developed to eliminate this time consuming process, so the entire cassette with wafers was dipped into wet etching and wet cleaning tanks. When wafer sizes increased to 100 mm, the entire cassette would often not be dipped as uniformly, and the quality of the results across the wafer became hard to control. By the time 150 mm wafers arrived, the cassettes were not dipped and were only used as wafer carriers and holders to store wafers, and robotics became prevalent for handling wafers. With 200 mm wafers manual handling of wafer cassettes becomes risky as they are heavier.[44]

In the 1970s, several companies migrated their semiconductor manufacturing technology from bipolar to MOSFET technology. Semiconductor manufacturing equipment has been considered costly since 1978.[45]

In 1984, KLA developed the first automatic reticle and photomask inspection tool.[46] In 1985, KLA developed an automatic inspection tool for silicon wafers, which replaced manual microscope inspection.[47]

In 1985, SGS (now STmicroelectronics) invented BCD, also called BCDMOS, a semiconductor manufacturing process using bipolar, CMOS and DMOS devices.[48] Applied Materials developed the first practical multi chamber, or cluster wafer processing tool, the Precision 5000.[49]

Until the 1980s, physical vapor deposition was the primary technique used for depositing materials onto wafers, until the advent of chemical vapor deposition.[50] Equipment with diffusion pumps was replaced with those using turbomolecular pumps as the latter do not use oil which often contaminated wafers during processing in vacuum.[51]

200 mm diameter wafers were first used in 1990 and became the standard until the introduction of 300 mm diameter wafers in 2000.[52][53] Bridge tools were used in the transition from 150 mm wafers to 200 mm wafers[54] and in the transition from 200 mm to 300 mm wafers.[55][56] The semiconductor industry has adopted larger wafers to cope with the increased demand for chips as larger wafers provide more surface area per wafer.[57] Over time, the industry shifted to 300 mm wafers which brought along the adoption of FOUPs,[58] but many products that are not advanced are still produced in 200 mm wafers such as analog ICs, RF chips, power ICs, BCDMOS and MEMS devices.[59]

Some processes such as cleaning,[60] ion implantation,[61][62] etching,[63] annealing[64] and oxidation[65] started to adopt single wafer processing instead of batch wafer processing in order to improve the reproducibility of results.[66][67] A similar trend existed in MEMS manufacturing.[68] In 1998, Applied Materials introduced the Producer, a cluster tool that had chambers grouped in pairs for processing wafers, which shared common vacuum and supply lines but were otherwise isolated, which was revolutionary at the time as it offered higher productivity than other cluster tools without sacrificing quality, due to the isolated chamber design.[69][54]

21st century

[edit]

The semiconductor industry is a global business today. The leading semiconductor manufacturers typically have facilities all over the world. Samsung Electronics, the world's largest manufacturer of semiconductors, has facilities in South Korea and the US. Intel, the second-largest manufacturer, has facilities in Europe and Asia as well as the US. TSMC, the world's largest pure play foundry, has facilities in Taiwan, China, Singapore, and the US. Qualcomm and Broadcom are among the biggest fabless semiconductor companies, outsourcing their production to companies like TSMC.[70] They also have facilities spread in different countries. As the average utilization of semiconductor devices increased, durability became an issue and manufacturers started to design their devices to ensure they last for enough time, and this depends on the market the device is designed for. This especially became a problem at the 10 nm node.[71][72]

Silicon on insulator (SOI) technology has been used in AMD's 130 nm, 90 nm, 65 nm, 45 nm and 32 nm single, dual, quad, six and eight core processors made since 2001.[73] During the transition from 200 mm to 300 mm wafers in 2001, many bridge tools were used which could process both 200 mm and 300 mm wafers.[74] At the time, 18 companies could manufacture chips in the leading edge 130nm process.[75]

In 2006, 450 mm wafers were expected to be adopted in 2012, and 675 mm wafers were expected to be used by 2021.[76]

Since 2009, "node" has become a commercial name for marketing purposes that indicates new generations of process technologies, without any relation to gate length, metal pitch or gate pitch.[77][78][79] For example, GlobalFoundries' 7 nm process was similar to Intel's 10 nm process, thus the conventional notion of a process node has become blurred.[80] Additionally, TSMC and Samsung's 10 nm processes are only slightly denser than Intel's 14 nm in transistor density. They are actually much closer to Intel's 14 nm process than they are to Intel's 10 nm process (e.g. Samsung's 10 nm processes' fin pitch is the exact same as that of Intel's 14 nm process: 42 nm).[81][82] Intel has changed the name of its 10 nm process to position it as a 7 nm process.[83] As transistors become smaller, new effects start to influence design decisions such as self-heating of the transistors, and other effects such as electromigration have become more evident since the 16nm node.[84][85]

In 2011, Intel demonstrated Fin field-effect transistors (FinFETs), where the gate surrounds the channel on three sides, allowing for increased energy efficiency and lower gate delay—and thus greater performance—over planar transistors at the 22nm node, because planar transistors which only have one surface acting as a channel, started to suffer from short channel effects.[86][87][88][89][90] A startup called SuVolta created a technology called Deeply Depleted Channel (DDC) to compete with FinFET transistors, which uses planar transistors at the 65 nm node which are very lightly doped.[91]

By 2018, a number of transistor architectures had been proposed for the eventual replacement of FinFET, most of which were based on the concept of GAAFET:[92] horizontal and vertical nanowires, horizontal nanosheet transistors[93][94] (Samsung MBCFET, Intel Nanoribbon), vertical FET (VFET) and other vertical transistors,[95][96] complementary FET (CFET), stacked FET, vertical TFETs, FinFETs with III-V semiconductor materials (III-V FinFET),[97][98] several kinds of horizontal gate-all-around transistors such as nano-ring, hexagonal wire, square wire, and round wire gate-all-around transistors[99] and negative-capacitance FET (NC-FET) which uses drastically different materials.[100] FD-SOI was seen as a potential low cost alternative to FinFETs.[101]

As of 2019, 14 nanometer and 10 nanometer chips are in mass production by Intel, UMC, TSMC, Samsung, Micron, SK Hynix, Toshiba Memory and GlobalFoundries, with 7 nanometer process chips in mass production by TSMC and Samsung, although their 7 nanometer node definition is similar to Intel's 10 nanometer process. The 5 nanometer process began being produced by Samsung in 2018.[102] As of 2019, the node with the highest transistor density is TSMC's 5 nanometer N5 node,[103] with a density of 171.3 million transistors per square millimeter.[104] In 2019, Samsung and TSMC announced plans to produce 3 nanometer nodes. GlobalFoundries has decided to stop the development of new nodes beyond 12 nanometers in order to save resources, as it has determined that setting up a new fab to handle sub-12 nm orders would be beyond the company's financial abilities.[105]

From 2020 to 2022, there was a global chip shortage. During this shortage caused by the COVID-19 pandemic, many semiconductor manufacturers banned employees from leaving company grounds.[106] Many countries granted subsidies to semiconductor companies for building new fabrication plants or fabs. Many companies were affected by counterfeit chips.[107] Semiconductors have become vital to the world economy and the national security of some countries.[108][109][110] The US has asked TSMC to not produce semiconductors for Huawei, a Chinese company.[111][112][113] CFET transistors were explored, which stacks NMOS and PMOS transistors on top of each other. Two approaches were evaluated for constructing these transistors: a monolithic approach which built both types of transistors in one process, and a sequential approach which built the two types of transistors separately and then stacked them.[114]

List of steps

[edit]This is a list of processing techniques that are employed numerous times throughout the construction of a modern electronic device; this list does not necessarily imply a specific order, nor that all techniques are taken during manufacture as, in practice the order and which techniques are applied, are often specific to process offerings by foundries, or specific to an integrated device manufacturer (IDM) for their own products, and a semiconductor device might not need all techniques. Equipment for carrying out these processes is made by a handful of companies. All equipment needs to be tested before a semiconductor fabrication plant is started.[115] These processes are done after integrated circuit design. A semiconductor fab operates 24/7[116] and many fabs use large amounts of water, primarily for rinsing the chips.[117]

- Wafer processing (also called front end)[118]

- Wet cleans

- Cleaning by solvents such as acetone, trichloroethylene or ultrapure water sometimes while spinning the wafer

- Piranha solution

- RCA clean

- Wafer scrubbing

- Spin cleaning[119]

- Jet spray cleaning[119]

- Cryogenic aerosol[120]

- Megasonics[121]

- Immersion batch cleaning[122]

- Surface passivation

- Photolithography

- Photoresist coating (often as a liquid, on the entire wafer)

- Photoresist baking (solidification in an oven)

- Edge bead removal[123][124]

- Exposure (in a photolithography stepper, scanner or mask aligner)

- Post Exposure Baking (PEB) improves the durability of the photoresist

- Development (removal of parts of the resist by application of a liquid developer, leaving only parts of the wafer exposed for ion implantation, layer deposition, etching, etc)

- Ion implantation (in which dopants are embedded in the wafer creating regions of increased or decreased conductivity)

- Etching (microfabrication)

- Dry etching (plasma etching)

- Reactive-ion etching (RIE)

- Deep reactive-ion etching (DRIE)

- Atomic layer etching (ALE)

- Reactive-ion etching (RIE)

- Wet etching

- Dry etching (plasma etching)

- Chemical vapor deposition (CVD)

- Metal organic chemical vapor deposition (MOCVD), used in LEDs

- Atomic layer deposition (ALD)

- Physical vapor deposition (PVD)

- Sputtering

- Evaporation

- Epitaxy[114][126]

- Ion beam deposition[128]

- Plasma ashing (for complete photoresist removal/photoresist stripping, also known as dry strip,[129] historically done with a chemical solvent called a resist stripper,[130] [131] to allow wafers to undergo another round of photolithography)

- Thermal treatments

- Rapid thermal processing (RTP), rapid thermal anneal

- Millisecond thermal processing, millisecond anneal, millisecond processing, flash lamp anneal (FLA)

- Laser anneal

- Furnace anneals

- Thermal oxidation

- Laser lift-off (for LED production[132])

- Electrochemical deposition (ECD). See Electroplating.

- Chemical-mechanical polishing (CMP)

- Wafer testing (where the electrical performance is verified using automatic test equipment, binning and/or laser trimming may also be carried out at this step)

- Wet cleans

- Die preparation

- Through-silicon via manufacture (for three-dimensional integrated circuits)

- Wafer mounting (wafer is mounted onto a metal frame using dicing tape)

- Wafer backgrinding and polishing[133] (reduces the thickness of the wafer for thin devices like a smartcard or PCMCIA card or wafer bonding and stacking, this can also occur during wafer dicing, in a process known as Dice Before Grind or DBG[134][135])

- Wafer bonding and stacking (for three-dimensional integrated circuits and MEMS)

- Redistribution layer manufacture (for WLCSP packages)

- Wafer bumping (for flip chip BGA (ball grid array), and WLCSP packages)

- Die cutting or wafer dicing

- IC packaging

- Die attachment (The die is attached to a leadframe using conductive paste or die attach film.[136][137])

- IC bonding: Wire bonding, thermosonic bonding, flip chip or tape automated bonding (TAB)

- IC encapsulation or integrated heat spreader (IHS) installation

- Molding (using special plastic molding compound that may contain glass powder as filler to control thermal expansion)

- Baking

- Electroplating (plates the copper leads of the lead frames with tin to make soldering easier)

- Laser marking or silkscreen printing

- Trim and form (separates the lead frames from each other, and bends the lead frame's pins so that they can be mounted on a printed circuit board)

- IC testing

Additionally steps such as Wright etch may be carried out.

Prevention of contamination and defects

[edit]When feature widths were far greater than about 10 micrometres, semiconductor purity was not as big of an issue as it is today in device manufacturing. In the 1960s, workers could work on semiconductor devices in street clothing.[138] As devices become more integrated, cleanrooms must become even cleaner. Today, fabrication plants are pressurized with filtered air to remove even the smallest particles, which could come to rest on the wafers and contribute to defects. The ceilings of semiconductor cleanrooms have fan filter units (FFUs) at regular intervals to constantly replace and filter the air in the cleanroom; semiconductor capital equipment may also have their own FFUs to clean air in the equipment's EFEM which allows the equipment to receive wafers in FOUPs. The FFUs, combined with raised floors with grills, help ensure a laminar air flow, to ensure that particles are immediately brought down to the floor and do not stay suspended in the air due to turbulence. The workers in a semiconductor fabrication facility are required to wear cleanroom suits to protect the devices from contamination by humans.[139] To increase yield, FOUPs and semiconductor capital equipment may have a mini environment with ISO class 1 level of dust, and FOUPs can have an even cleaner micro environment.[11][8] FOUPs and SMIF pods isolate the wafers from the air in the cleanroom, increasing yield because they reduce the number of defects caused by dust particles. Also, fabs have as few people as possible in the cleanroom to make maintaining the cleanroom environment easier, since people, even when wearing cleanroom suits, shed large amounts of particles, especially when walking.[140][139][141]

Wafers

[edit]A typical wafer is made out of extremely pure silicon that is grown into mono-crystalline cylindrical ingots (boules) up to 300 mm (slightly less than 12 inches) in diameter using the Czochralski process. These ingots are then sliced into wafers about 0.75 mm thick and polished to obtain a very regular and flat surface. During the production process wafers are often grouped into lots, which are represented by a FOUP, SMIF or a wafer cassette, which are wafer carriers. FOUPs and SMIFs can be transported in the fab between machines and equipment with an automated OHT (Overhead Hoist Transport) AMHS (Automated Material Handling System).[58] Besides SMIFs and FOUPs, wafer cassettes can be placed in a wafer box or a wafer carrying box.[142]

Processing

[edit]In semiconductor device fabrication, the various processing steps fall into four general categories: deposition, removal, patterning, and modification of electrical properties.

- Deposition is any process that grows, coats, or otherwise transfers a material onto the wafer. Available technologies include physical vapor deposition (PVD), chemical vapor deposition (CVD), electrochemical deposition (ECD), molecular beam epitaxy (MBE), and more recently, atomic layer deposition (ALD) among others. Deposition can be understood to include oxide layer formation, by thermal oxidation or, more specifically, LOCOS.

- Removal is any process that removes material from the wafer; examples include etch processes (either wet or dry) and chemical-mechanical planarization (CMP).

- Patterning is the shaping or altering of deposited materials, and is generally referred to as lithography. For example, in conventional lithography, the wafer is coated with a chemical called a photoresist; then, a machine called an aligner or stepper focuses a mask image on the wafer using short-wavelength light; the exposed regions (for "positive" resist) are washed away by a developer solution. The wafer then undergoes etching where materials not protected by the mask are removed. After removal or other processing, the remaining photoresist is removed by "dry" stripping/plasma ashing/resist ashing or by "wet" resist stripper chemistry.[143] Wet etching was widely used in the 1960s and 1970s,[144][145] but it was replaced by dry etching/plasma etching starting at the 10 micron to 3 micron nodes.[146][147] This is because wet etching makes undercuts (etching under mask layers or resist layers with patterns).[148][149][150] Dry etching has become the dominant etching technique.[151]

- Modification of electrical properties has historically entailed doping transistor sources and drains and polysilicon. Doping consists of introducing impurities into the atomic structure of a semiconductor material, in order to modify its electrical properties. Initially thermal diffusion with furnaces at 900-1200°C with gases containing dopants were used for doping wafers[152][153][154] and there was resistance against ion implantation as it still required a separate furnace[155] but ion implantation ultimately prevailed in the 1970s[156] as it offers better reproducibility of results.[38] Ion implantation is practical because of the high sensitivity of semiconductor devices to foreign atoms, as ion implantation does not deposit large numbers of atoms.[38] Doping processes with ion implantation are followed by furnace annealing[157][38] or, in advanced devices, by rapid thermal annealing (RTA) to activate the dopants. Annealing was initially done at 500 to 700°C, but this was later increased to 900 to 1100°C. Implanters can either process a single wafer at a time or several, up to 17, mounted on a rotating disk.[38]

Modification of electrical properties now also extends to the reduction of a material's dielectric constant in low-κ insulators via exposure to ultraviolet light in UV processing (UVP). Modification is frequently achieved by oxidation, which can be carried out to create semiconductor-insulator junctions, such as in the local oxidation of silicon (LOCOS) to fabricate metal oxide field effect transistors. Modern chips have up to eleven or more metal levels produced in over 300 or more sequenced processing steps.

A recipe in semiconductor manufacturing is a list of conditions under which a wafer will be processed by a particular machine in a processing step during manufacturing.[158] Process variability is a challenge in semiconductor processing, in which wafers are not processed evenly or the quality or effectiveness of processes carried out on a wafer are not even across the wafer surface.[159]

Front-end-of-line (FEOL) processing

[edit]Wafer processing is separated into FEOL and BEOL stages. FEOL processing refers to the formation of the transistors directly in the silicon. The raw wafer is engineered by the growth of an ultrapure, virtually defect-free silicon layer through epitaxy.[160][161] In the most advanced logic devices, prior to the silicon epitaxy step, tricks are performed to improve the performance of the transistors to be built. One method involves introducing a straining step wherein a silicon variant such as silicon-germanium (SiGe) is deposited. Once the epitaxial silicon is deposited, the crystal lattice becomes stretched somewhat, resulting in improved electronic mobility. Another method, called silicon on insulator technology involves the insertion of an insulating layer between the raw silicon wafer and the thin layer of subsequent silicon epitaxy. This method results in the creation of transistors with reduced parasitic effects. Semiconductor equipment may have several chambers which process wafers in processes such as deposition and etching. Many pieces of equipment handle wafers between these chambers in an internal nitrogen or vacuum environment to improve process control.[3] Wet benches with tanks containing chemical solutions were historically used for cleaning and etching wafers.[162]

At the 90nm node, transistor channels made with strain engineering were introduced to improve drive current in PMOS transistors by introducing regions with Silicon-Germanium in the transistor. The same was done in NMOS transistors at the 20nm node.[126]

In 2007, HKMG (high-k/metal gate) transistors were introduced by Intel at the 45nm node, which replaced polysilicon gates which in turn replaced metal gate (aluminum gate)[163] technology in the 1970s.[164] High-k dielectric such as hafnium oxide (HfO2) replaced silicon oxynitride (SiON), in order to prevent large amounts of leakage current in the transistor while allowing for continued scaling or shrinking of the transistors. However HfO2 is not compatible with polysilicon gates which requires the use of a metal gate. Two approaches were used in production: gate-first and gate-last. Gate-first consists of depositing the high-k dielectric and then the gate metal such as Tantalum nitride whose workfunction depends on whether the transistor is NMOS or PMOS, polysilicon deposition, gate line patterning, source and drain ion implantation, dopant anneal, and silicidation of the polysilicon and the source and drain.[165][166] In DRAM memories this technology was first adopted in 2015.[167]

Gate-last consisted of first depositing the High-κ dielectric, creating dummy gates, manufacturing sources and drains by ion deposition and dopant annealing, depositing an "interlevel dielectric (ILD)" and then polishing, and removing the dummy gates to replace them with a metal whose workfunction depended on whether the transistor was NMOS or PMOS, thus creating the metal gate. A third process, full silicidation (FUSI)[168] was not pursued due to manufacturing problems.[169] Gate-first became dominant at the 22nm/20nm node.[170][171] HKMG has been extended from planar transistors for use in FinFET and nanosheet transistors.[172] Hafnium silicon oxynitride can also be used instead of Hafnium oxide.[173][174][3][175][176]

Since the 16nm/14nm node, Atomic layer etching (ALE) is increasingly used for etching as it offers higher precision than other etching methods. In production, plasma ALE is commonly used, which removes materials unidirectionally, creating structures with vertical walls. Thermal ALE can also be used to remove materials isotropically, in all directions at the same time but without the capability to create vertical walls. Plasma ALE was initially adopted for etching contacts in transistors, and since the 7nm node it is also used to create transistor structures by etching them.[125]

Gate oxide and implants

[edit]Front-end surface engineering is followed by growth of the gate dielectric (traditionally silicon dioxide), patterning of the gate, patterning of the source and drain regions, and subsequent implantation or diffusion of dopants to obtain the desired complementary electrical properties. In dynamic random-access memory (DRAM) devices, storage capacitors are also fabricated at this time, typically stacked above the access transistor (the now defunct DRAM manufacturer Qimonda implemented these capacitors with trenches etched deep into the silicon surface).

Back-end-of-line (BEOL) processing

[edit]Metal layers

[edit]Once the various semiconductor devices have been created, they must be interconnected to form the desired electrical circuits. This occurs in a series of wafer processing steps collectively referred to as BEOL (not to be confused with back end of chip fabrication, which refers to the packaging and testing stages). BEOL processing involves creating metal interconnecting wires that are isolated by dielectric layers. The insulating material has traditionally been a form of SiO2 or a silicate glass, but recently new low dielectric constant materials, also called low-κ dielectrics, are being used (such as silicon oxycarbide), typically providing dielectric constants around 2.7 (compared to 3.82 for SiO2), although materials with constants as low as 2.2 are being offered to chipmakers.

BEoL has been used since 1995 at the 350nm and 250nm nodes (0.35 and 0.25 micron nodes), at the same time chemical mechanical polishing began to be employed. At the time, 2 metal layers for interconnect, also called metallization[177] was state-of-the-art.[178]

Since the 22nm node, some manufacturers have added a new process called middle-of-line (MOL) which connects the transistors to the rest of the interconnect made in the BEoL process. The MOL is often based on tungsten and has upper and lower layers: the lower layer connects the junctions of the transistors, and an upper layer which is a tungsten plug that connects the transistors to the interconnect. Intel at the 10nm node introduced contact-over-active-gate (COAG) which, instead of placing the contact for connecting the transistor close to the gate of the transistor, places it directly over the gate of the transistor to improve transistor density.[179]

Interconnect

[edit]

Historically, the metal wires have been composed of aluminum. In this approach to wiring (often called subtractive aluminum), blanket films of aluminum are deposited first, patterned, and then etched, leaving isolated wires. Dielectric material is then deposited over the exposed wires. The various metal layers are interconnected by etching holes (called "vias") in the insulating material and then depositing tungsten in them with a CVD technique using tungsten hexafluoride; this approach can still be (and often is) used in the fabrication of many memory chips such as dynamic random-access memory (DRAM), because the number of interconnect levels can be small (no more than four). The aluminum was sometimes alloyed with copper for preventing recrystallization. Gold was also used in interconnects in early chips.[180]

More recently, as the number of interconnect levels for logic has substantially increased due to the large number of transistors that are now interconnected in a modern microprocessor, the timing delay in the wiring has become so significant as to prompt a change in wiring material (from aluminum to copper interconnect layer)[181] alongside a change in dielectric material in the interconnect (from silicon dioxides to newer low-κ insulators).[182][183] This performance enhancement also comes at a reduced cost via damascene processing, which eliminates processing steps. As the number of interconnect levels increases, planarization of the previous layers is required to ensure a flat surface prior to subsequent lithography. Without it, the levels would become increasingly crooked, extending outside the depth of focus of available lithography, and thus interfering with the ability to pattern. CMP (chemical-mechanical planarization) is the primary processing method to achieve such planarization, although dry etch back is still sometimes employed when the number of interconnect levels is no more than three. Copper interconnects use an electrically conductive barrier layer to prevent the copper from diffusing into ("poisoning") its surroundings, often made of tantalum nitride.[184][179] In 1997, IBM was the first to adopt copper interconnects.[185]

In 2014, Applied Materials proposed the use of cobalt in interconnects at the 22nm node, used for encapsulating copper interconnects in cobalt to prevent electromigration, replacing tantalum nitride since it needs to be thicker than cobalt in this application.[179][186]

Wafer metrology

[edit]The highly serialized nature of wafer processing has increased the demand for metrology in between the various processing steps. For example, thin film metrology based on ellipsometry or reflectometry is used to tightly control the thickness of gate oxide, as well as the thickness, refractive index, and extinction coefficient of photoresist and other coatings.[187] Wafer metrology equipment/tools, or wafer inspection tools are used to verify that the wafers haven't been damaged by previous processing steps up until testing; if too many dies on one wafer have failed, the entire wafer is scrapped to avoid the costs of further processing. Virtual metrology has been used to predict wafer properties based on statistical methods without performing the physical measurement itself.[1]

Device test

[edit]Once the front-end process has been completed, the semiconductor devices or chips are subjected to a variety of electrical tests to determine if they function properly. The percent of devices on the wafer found to perform properly is referred to as the yield. Manufacturers are typically secretive about their yields,[188] but it can be as low as 30%, meaning that only 30% of the chips on the wafer work as intended. Process variation is one among many reasons for low yield. Testing is carried out to prevent faulty chips from being assembled into relatively expensive packages.

The yield is often but not necessarily related to device (die or chip) size. As an example, in December 2019, TSMC announced an average yield of ~80%, with a peak yield per wafer of >90% for their 5nm test chips with a die size of 17.92 mm2. The yield went down to 32% with an increase in die size to 100 mm2.[189] The number of killer defects on a wafer, regardless of die size, can be noted as the defect density (or D0) of the wafer per unit area, usually cm2.

The fab tests the chips on the wafer with an electronic tester that presses tiny probes against the chip. The machine marks each bad chip with a drop of dye. Currently, electronic dye marking is possible if wafer test data (results) are logged into a central computer database and chips are "binned" (i.e. sorted into virtual bins) according to predetermined test limits such as maximum operating frequencies/clocks, number of working (fully functional) cores per chip, etc. The resulting binning data can be graphed, or logged, on a wafer map to trace manufacturing defects and mark bad chips. This map can also be used during wafer assembly and packaging. Binning allows chips that would otherwise be rejected to be reused in lower-tier products, as is the case with GPUs and CPUs, increasing device yield, especially since very few chips are fully functional (have all cores functioning correctly, for example). eFUSEs may be used to disconnect parts of chips such as cores, either because they did not work as intended during binning, or as part of market segmentation (using the same chip for low, mid and high-end tiers). Chips may have spare parts to allow the chip to fully pass testing even if it has several non-working parts.

Chips are also tested again after packaging, as the bond wires may be missing, or analog performance may be altered by the package. This is referred to as the "final test". Chips may also be imaged using x-rays.

Usually, the fab charges for testing time, with prices on the order of cents per second. Testing times vary from a few milliseconds to a couple of seconds, and the test software is optimized for reduced testing time. Multiple chip (multi-site) testing is also possible because many testers have the resources to perform most or all of the tests in parallel and on several chips at once.

Chips are often designed with "testability features" such as scan chains or a "built-in self-test" to speed testing and reduce testing costs. In certain designs that use specialized analog fab processes, wafers are also laser-trimmed during testing, in order to achieve tightly distributed resistance values as specified by the design.

Good designs try to test and statistically manage corners (extremes of silicon behavior caused by a high operating temperature combined with the extremes of fab processing steps). Most designs cope with at least 64 corners.

Device yield

[edit]Device yield or die yield is the number of working chips or dies on a wafer, given in percentage since the number of chips on a wafer (Die per wafer, DPW) can vary depending on the chips' size and the wafer's diameter. Yield degradation is a reduction in yield, which historically was mainly caused by dust particles, however since the 1990s, yield degradation is mainly caused by process variation, the process itself and by the tools used in chip manufacturing, although dust still remains a problem in many older fabs. Dust particles have an increasing effect on yield as feature sizes are shrunk with newer processes. Automation and the use of mini environments inside of production equipment, FOUPs and SMIFs have enabled a reduction in defects caused by dust particles. Device yield must be kept high to reduce the selling price of the working chips since working chips have to pay for those chips that failed, and to reduce the cost of wafer processing. Yield can also be affected by the design and operation of the fab.

Tight control over contaminants and the production process are necessary to increase yield. Contaminants may be chemical contaminants or be dust particles. "Killer defects" are those caused by dust particles that cause complete failure of the device (such as a transistor). There are also harmless defects. A particle needs to be 1/5 the size of a feature to cause a killer defect. So if a feature is 100 nm across, a particle only needs to be 20 nm across to cause a killer defect. Electrostatic electricity can also affect yield adversely. Chemical contaminants or impurities include heavy metals such as iron, copper, nickel, zinc, chromium, gold, mercury and silver, alkali metals such as sodium, potassium and lithium, and elements such as aluminum, magnesium, calcium, chlorine, sulfur, carbon, and fluorine. It is important for these elements to not remain in contact with the silicon, as they could reduce yield. Chemical mixtures may be used to remove these elements from the silicon; different mixtures are effective against different elements.

Several models are used to estimate yield. They are Murphy's model, Poisson's model, the binomial model, Moore's model and Seeds' model. There is no universal model; a model has to be chosen based on actual yield distribution (the location of defective chips). For example, Murphy's model assumes that yield loss occurs more at the edges of the wafer (non-working chips are concentrated on the edges of the wafer), Poisson's model assumes that defective dies are spread relatively evenly across the wafer, and Seeds's model assumes that defective dies are clustered together.[190]

Smaller dies cost less to produce (since more fit on a wafer, and wafers are processed and priced as a whole), and can help achieve higher yields since smaller dies have a lower chance of having a defect, due to their lower surface area on the wafer. However, smaller dies require smaller features to achieve the same functions of larger dies or surpass them, and smaller features require reduced process variation and increased purity (reduced contamination) to maintain high yields. Metrology tools are used to inspect the wafers during the production process and predict yield, so wafers predicted to have too many defects may be scrapped to save on processing costs.[188]

Die preparation

[edit]Once tested, a wafer is typically reduced in thickness in a process also known as "backlap",[118]: 6 "backfinish", "wafer backgrind" or "wafer thinning"[191] before the wafer is scored and then broken into individual dies, a process known as wafer dicing. Only the good, unmarked chips are packaged.

Packaging

[edit]After the dies are tested for functionality and binned, they are packaged. Plastic or ceramic packaging involves mounting the die, connecting the die/bond pads to the pins on the package, and sealing the die. Tiny bondwires are used to connect the pads to the pins. In the 'old days' (1970s), wires were attached by hand, but now specialized machines perform the task. Traditionally, these wires have been composed of gold, leading to a lead frame (pronounced "leed frame") of solder-plated copper; lead is poisonous, so lead-free "lead frames" are now mandated by RoHS. Traditionally the bond pads are located on the edges of the die, however, Flip-chip packaging can be used to place bond pads across the entire surface of the die.

Chip scale package (CSP) is another packaging technology. A plastic dual in-line package, like most packages, is many times larger than the actual die hidden inside, whereas CSP chips are nearly the size of the die; a CSP can be constructed for each die before the wafer is diced.

The packaged chips are retested to ensure that they were not damaged during packaging and that the die-to-pin interconnect operation was performed correctly. A laser then etches the chip's name and numbers on the package. The steps involving testing and packaging of dies, followed by final testing of finished, packaged chips, are called the back end,[118] post-fab,[192] ATMP (Assembly, Test, Marking, and Packaging)[193] or ATP (Assembly, Test and Packaging) of semiconductor manufacturing, and may be carried out by OSAT (OutSourced Assembly and Test) companies which are separate from semiconductor foundries. A foundry is a company or fab performing manufacturing processes such as photolithography and etching that are part of the front end of semiconductor manufacturing.[194][195]

Hazardous materials

[edit]Many toxic materials are used in the fabrication process.[196] These include:

- poisonous elemental dopants, such as arsenic, antimony, and phosphorus.

- poisonous compounds, such as arsine and phosphine in ion implantation doping, tungsten hexafluoride, used in CVD deposition of tungsten in transistor interconnects, and silane used for depositing polysilicon.[197]

- highly reactive liquids, such as hydrogen peroxide, fuming nitric acid, sulfuric acid, and hydrofluoric acid, used in etching and cleaning.

It is vital that workers not be directly exposed to these dangerous substances. The high degree of automation common in the IC fabrication industry helps to reduce the risks of exposure. Most fabrication facilities employ exhaust management systems, such as wet scrubbers, combustors, heated absorber cartridges, etc.,[198][199][200] to control the risk to workers and to the environment.

Timeline of commercial MOSFET nodes

[edit]See also

[edit]- Deathnium

- Glossary of microelectronics manufacturing terms

- List of semiconductor scale examples

- MOSFET

- Multigate device

- Semiconductor industry

- International Technology Roadmap for Semiconductors

- Semiconductor consolidation

- Local oxidation of silicon (LOCOS)

- List of integrated circuit manufacturers

- List of semiconductor fabrication plants

- Microfabrication

- Semiconductor Equipment and Materials International (SEMI)—the semiconductor industry trade association

- SEMI font for labels on wafers

- Etch pit density

- Passivation

- Planar process

- Transistor count

References

[edit]- ^ a b Hendrik Purwins; Bernd Barak; Ahmed Nagi; Reiner Engel; Uwe Höckele; Andreas Kyek; Srikanth Cherla; Benjamin Lenz; Günter Pfeifer; Kurt Weinzierl (2014). "Regression Methods for Virtual Metrology of Layer Thickness in Chemical Vapor Deposition". IEEE/ASME Transactions on Mechatronics. 19 (1): 1–8. doi:10.1109/TMECH.2013.2273435. S2CID 12369827. Retrieved November 9, 2015.

- ^ "8 Things You Should Know About Water & Semiconductors". China Water Risk. 11 July 2013. Retrieved 2023-01-21.

- ^ a b c d e Yoshio, Nishi (2017). Handbook of Semiconductor Manufacturing Technology. CRC Press.

- ^ Lei, Wei-Sheng; Kumar, Ajay; Yalamanchili, Rao (2012-04-06). "Die singulation technologies for advanced packaging: A critical review". Journal of Vacuum Science & Technology B, Nanotechnology and Microelectronics: Materials, Processing, Measurement, and Phenomena. 30 (4): 040801. Bibcode:2012JVSTB..30d0801L. doi:10.1116/1.3700230. ISSN 2166-2746.

- ^ a b Wang, H. P.; Kim, S. C.; Liu, B. (2014). Advanced FOUP purge using diffusers for FOUP door-off application. 25th Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC 2014). pp. 120–124. doi:10.1109/ASMC.2014.6846999. ISBN 978-1-4799-3944-2. S2CID 2482339.

- ^ a b 450mm FOUP/LPU system in advanced semiconductor manufacturing processes: A study on the minimization of oxygen content inside FOUP when the door is opened. 2015 Joint e-Manufacturing and Design Collaboration Symposium (eMDC) & 2015 International Symposium on Semiconductor Manufacturing (ISSM).

- ^ Lin, Tee; Fu, Ben-Ran; Hu, Shih-Cheng; Tang, Yi-Han (2018). "Moisture Prevention in a Pre-Purged Front-Opening Unified Pod (FOUP) During Door Opening in a Mini-Environment". IEEE Transactions on Semiconductor Manufacturing. 31 (1): 108–115. doi:10.1109/TSM.2018.2791985. S2CID 25469704.

- ^ a b Kure, Tokuo; Hanaoka, Hideo; Sugiura, Takumi; Nakagawa, Shinya (2007). "Clean-room Technologies for the Mini-environment Age" (PDF). Hitachi Review. 56 (3): 70–74. CiteSeerX 10.1.1.493.1460. S2CID 30883737. Archived (PDF) from the original on 2021-11-01. Retrieved 2021-11-01.

- ^ Kim, Seong Chan; Schelske, Greg (2016). FOUP purge performance improvement using EFEM flow converter. 2016 27th Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC). pp. 6–11. doi:10.1109/ASMC.2016.7491075. ISBN 978-1-5090-0270-2. S2CID 3240442.

- ^ Benalcazar, David; Lin, Tee; Hu, Ming-Hsuan; Ali Zargar, Omid; Lin, Shao-Yu; Shih, Yang-Cheng; Leggett, Graham (2022). "A Numerical Study on the Effects of Purge and Air Curtain Flow Rates on Humidity Invasion Into a Front Opening Unified Pod (FOUP)". IEEE Transactions on Semiconductor Manufacturing. 35 (4): 670–679. doi:10.1109/TSM.2022.3209221. S2CID 252555815.

- ^ a b Lin, Tee; Ali Zargar, Omid; Juina, Oscar; Lee, Tzu-Chieh; Sabusap, Dexter Lyndon; Hu, Shih-Cheng; Leggett, Graham (2020). "Performance of Different Front-Opening Unified Pod (FOUP) Moisture Removal Techniques With Local Exhaust Ventilation System". IEEE Transactions on Semiconductor Manufacturing. 33 (2): 310–315. doi:10.1109/TSM.2020.2977122. S2CID 213026336.

- ^ Nishi, Yoshio; Doering, Robert (19 December 2017). Handbook of Semiconductor Manufacturing Technology. CRC Press. ISBN 978-1-4200-1766-3.

- ^ Mack, Chris (11 March 2008). Fundamental Principles of Optical Lithography: The Science of Microfabrication. John Wiley & Sons. ISBN 978-0-470-72386-9.

- ^ Lambrechts, Wynand; Sinha, Saurabh; Abdallah, Jassem Ahmed; Prinsloo, Jaco (13 September 2018). Extending Moore's Law through Advanced Semiconductor Design and Processing Techniques. CRC Press. ISBN 978-1-351-24866-2.

- ^ Yu, Shimeng (19 April 2022). Semiconductor Memory Devices and Circuits. CRC Press. ISBN 978-1-000-56761-8.

- ^ a b Shirriff, Ken (June 2020). "Die shrink: How Intel scaled-down the 8086 processor". Retrieved 22 May 2022.

- ^ "Overall Roadmap Technology Characteristics" (PDF). Semiconductor Industry Association.

- ^ Shukla, Priyank. "A Brief History of Process Node Evolution". Design And Reuse.

- ^ "Technology Node - WikiChip". Archived from the original on 2020-11-12. Retrieved 2020-10-20.

- ^ a b Moore, Samuel K. (21 July 2020). "A Better Way To Measure Progress in Semiconductors". IEEE Spectrum: Technology, Engineering, and Science News. Retrieved 22 May 2022.

- ^ a b Ridley, Jacob (April 29, 2020). "Intel 10nm isn't bigger than AMD 7nm, you're just measuring wrong". PC Gamer. Archived from the original on October 28, 2020. Retrieved October 21, 2020.

- ^ Cutress, Ian. "Intel's 10nm Cannon Lake and Core i3-8121U Deep Dive Review". AnandTech. Archived from the original on 2020-11-12. Retrieved 2020-11-07.

- ^ "VLSI 2018: GlobalFoundries 12nm Leading-Performance, 12LP". 22 July 2018. Archived from the original on 7 April 2019. Retrieved 20 October 2020.

- ^ Frosch, C. J.; Derick, L (1957). "Surface Protection and Selective Masking during Diffusion in Silicon". Journal of the Electrochemical Society. 104 (9): 547. doi:10.1149/1.2428650.

- ^ Huff, Howard; Riordan, Michael (2007-09-01). "Frosch and Derick: Fifty Years Later (Foreword)". The Electrochemical Society Interface. 16 (3): 29. doi:10.1149/2.F02073IF. ISSN 1064-8208.

- ^ US2802760A, Lincoln, Derick & Frosch, Carl J., "Oxidation of semiconductive surfaces for controlled diffusion", issued 1957-08-13

- ^ Frosch, C. J.; Derick, L (1957). "Surface Protection and Selective Masking during Diffusion in Silicon". Journal of the Electrochemical Society. 104 (9): 547. doi:10.1149/1.2428650.

- ^ Moskowitz, Sanford L. (2016). Advanced Materials Innovation: Managing Global Technology in the 21st century. John Wiley & Sons. p. 168. ISBN 978-0-470-50892-3.

- ^ Christophe Lécuyer; David C. Brook; Jay Last (2010). Makers of the Microchip: A Documentary History of Fairchild Semiconductor. MIT Press. pp. 62–63. ISBN 978-0-262-01424-3.

- ^ Claeys, Cor L. (2003). ULSI Process Integration III: Proceedings of the International Symposium. The Electrochemical Society. pp. 27–30. ISBN 978-1-56677-376-8.

- ^ Lojek, Bo (2007). History of Semiconductor Engineering. Springer Science & Business Media. p. 120. ISBN 9783540342588.

- ^ US 3025589 Hoerni, J. A.: "Method of Manufacturing Semiconductor Devices” filed May 1, 1959

- ^ US 3064167 Hoerni, J. A.: "Semiconductor device" filed May 15, 1960

- ^ Howard R. Duff (2001). "John Bardeen and transistor physics". AIP Conference Proceedings. Vol. 550. pp. 3–32. doi:10.1063/1.1354371.

- ^ a b "1963: Complementary MOS Circuit Configuration is Invented". Computer History Museum. Archived from the original on 23 July 2019. Retrieved 6 July 2019.

- ^ Sah, Chih-Tang; Wanlass, Frank (February 1963). "Nanowatt logic using field-effect metal-oxide semiconductor triodes". 1963 IEEE International Solid-State Circuits Conference. Digest of Technical Papers. Vol. VI. pp. 32–33. doi:10.1109/ISSCC.1963.1157450.

- ^ Lojek, Bo (2007). History of Semiconductor Engineering. Springer Science & Business Media. p. 330. ISBN 9783540342588. Archived from the original on 2020-08-06. Retrieved 2019-07-21.

- ^ a b c d e Rubin, Leonard; Poate, John (June–July 2003). "Ion Implantation in Silicon Technology" (PDF). The Industrial Physicist. 9 (3). American Institute of Physics: 12–15.

- ^ Manasevit, H. M.; Simpson, W. J. (1964). "Single-Crystal Silicon on a Sapphire Substrate". Journal of Applied Physics. 35 (4): 1349–51. Bibcode:1964JAP....35.1349M. doi:10.1063/1.1713618.

- ^ Mueller, C. W.; Robinson, P. H. (December 1964). "Grown-film silicon transistors on sapphire". Proceedings of the IEEE. 52 (12): 1487–90. doi:10.1109/PROC.1964.3436.

- ^ Extending Moore's Law through Advanced Semiconductor Design and Processing Techniques. CRC Press. 13 September 2018. ISBN 978-1-351-24866-2.

- ^ "Evolution of the Silicon Wafer Infographic". Archived from the original on December 22, 2015.

- ^ How Transistor Area Shrank by 1 Million Fold. Springer. 15 July 2020. ISBN 978-3-030-40021-7.

- ^ Wafer Fabrication: Factory Performance and Analysis. Springer. 30 November 1995. ISBN 978-0-7923-9619-2.

- ^ "Wafer fab costs skyrocketing out of control".

- ^ "Kla 200 Series".

- ^ "KLA 2020 - the tool that sparked the yield management revolution".

- ^ "Three Chips in One: The History of the BCD Integrated Circuit - IEEE Spectrum". IEEE.

- ^ "Applied Materials Precision 5000 CVD System".

- ^ "Series 900 In-Line Sputtering System by MRC".

- ^ Vacuum Deposition onto Webs, Films and Foils. William Andrew. 21 June 2011. ISBN 978-1-4377-7868-7.

- ^ "The world's first 300 mm fab at Infineon - challenges and success". Proceedings of ISSM2000. Ninth International Symposium on Semiconductor Manufacturing (IEEE Cat. No.00CH37130). doi:10.1109/ISSM.2000.993612. S2CID 109383925.

- ^ "The 300mm Era Begins". 10 July 2000.

- ^ a b "Applied Materials Producer".

- ^ "300mm Semiconductor Wafers get a reprieve". Chip History.

- ^ "Novellus offers 300-mm CVD tool that's smaller than 200-mm, lower costs". 10 July 2000.

- ^ Huff, Howard R.; Goodall, Randal K.; Bullis, W. Murray; Moreland, James A.; Kirscht, Fritz G.; Wilson, Syd R.; The NTRS Starting Materials Team (24 November 1998). "Model-based silicon wafer criteria for optimal integrated circuit performance". AIP Conference Proceedings. Vol. 449. pp. 97–112. doi:10.1063/1.56795.

- ^ a b Zhang, Jie (24 September 2018). Wafer Fabrication: Automatic Material Handling System. Walter de Gruyter GmbH & Co KG. ISBN 978-3-11-048723-7.

- ^ LaPedus, Mark (May 21, 2018). "200mm Fab Crunch". Semiconductor Engineering.

- ^ Becker, Scott (24 March 2003). "The future of batch and single-wafer processing in wafer cleaning". EE Times.

- ^ "Manufacturing advantages of single wafer high current ion implantation". Proceedings of 11th International Conference on Ion Implantation Technology. doi:10.1109/IIT.1996.586424. S2CID 70599233.

- ^ Renau, A. (2005). "Approaches to single wafer high current ion implantation". Nuclear Instruments and Methods in Physics Research Section B: Beam Interactions with Materials and Atoms. 237 (1–2): 284–289. Bibcode:2005NIMPB.237..284R. doi:10.1016/j.nimb.2005.05.016.

- ^ Dry Etching for VLSI. Springer. 29 June 2013. ISBN 978-1-4899-2566-4.

- ^ Hossain-Pas, S.; Pas, M. F. (1997). "Understanding the Impact of Batch vs. Single Wafer in Thermal Processing Using Cost of Ownership Analysis". MRS Proceedings. 470. doi:10.1557/PROC-470-201.

- ^ Weimer, R.A.; Eppich, D.M.; Beaman, K.L.; Powell, D.C.; Gonzalez, F. (2003). "Contrasting single-wafer and batch processing for memory devices". IEEE Transactions on Semiconductor Manufacturing. 16 (2): 138–146. doi:10.1109/TSM.2003.810939.

- ^ Introduction to Microfabrication. John Wiley & Sons. 28 January 2005. ISBN 978-0-470-02056-2.

- ^ "Trends in single-wafer processing". 1992 Symposium on VLSI Technology Digest of Technical Papers. doi:10.1109/VLSIT.1992.200629. S2CID 110840307.

- ^ "Single Wafer vs Batch Wafer Processing in MEMS Manufacturing". 2 August 2016. Archived from the original on 18 February 2024. Retrieved 18 February 2024.

- ^ "Applied Materials Producer - a new revolution is upon us". Chip History.

- ^ "Top 10 Worldwide Semiconductor Sales Leaders - Q1 2017 - AnySilicon". AnySilicon. 2017-05-09. Archived from the original on 2017-11-06. Retrieved 2017-11-19.

- ^ Mutschler, Ann (July 13, 2017). "Transistor Aging Intensifies At 10/7nm And Below". Semiconductor Engineering.

- ^ Sperling, Ed (February 14, 2018). "Chip Aging Accelerates". Semiconductor Engineering.

- ^ de Vries, Hans. "Chip Architect: Intel and Motorola/AMD's 130 nm processes to be revealed". chip-architect.com. Retrieved 22 April 2018.

- ^ "'Bridge tools' appear to be taking over 300-mm movement". 26 April 2001.

- ^ "Foundry Wars Begin". 19 April 2021.

- ^ "Get ready for 675-mm fabs in 2021". 14 November 2006.

- ^ Shukla, Priyank. "A Brief History of Process Node Evolution". design-reuse.com. Archived from the original on 2019-07-09. Retrieved 2019-07-09.

- ^ Hruska, Joel (23 June 2014). "14nm, 7nm, 5nm: How low can CMOS go? It depends if you ask the engineers or the economists…". ExtremeTech. Archived from the original on 2019-07-09. Retrieved 2019-07-09.

- ^ "Exclusive: Is Intel Really Starting To Lose Its Process Lead? 7nm Node Slated For Release in 2022". wccftech.com. 2016-09-10. Archived from the original on 2019-07-09. Retrieved 2019-07-09.

- ^ "Life at 10nm. (Or is it 7nm?) And 3nm - Views on Advanced Silicon Platforms". eejournal.com. 2018-03-12. Archived from the original on 2019-07-09. Retrieved 2019-07-09.

- ^ "10 nm lithography process - WikiChip". en.wikichip.org. Archived from the original on 2019-07-01. Retrieved 2019-08-17.

- ^ "14 nm lithography process - WikiChip". en.wikichip.org. Archived from the original on 2019-07-01. Retrieved 2019-08-17.

- ^ Cutress, Ian. "Intel's Process Roadmap to 2025: With 4nm, 3nm, 20A and 18A?!". AnandTech.

- ^ Bailey, Brian (August 9, 2018). "Chip Aging Becomes Design Problem". Semiconductor Engineering.

- ^ Derbyshire, Katherine (April 20, 2017). "Will Self-Heating Stop FinFETs". Semiconductor Engineering.

- ^ "FinFET".

- ^ "Foundries Rush 3-D Transistors - IEEE Spectrum".

- ^ Bohr, Mark; Mistry, Kaizad (May 2011). "Intel's Revolutionary 22 nm Transistor Technology" (PDF). intel.com. Retrieved April 18, 2018.

- ^ Grabham, Dan (May 6, 2011). "Intel's Tri-Gate transistors: everything you need to know". TechRadar. Retrieved April 19, 2018.

- ^ Bohr, Mark T.; Young, Ian A. (2017). "CMOS Scaling Trends and Beyond". IEEE Micro. 37 (6): 20–29. doi:10.1109/MM.2017.4241347. S2CID 6700881.

The next major transistor innovation was the introduction of FinFET (tri-gate) transistors on Intel's 22-nm technology in 2011.

- ^ "Start-up Seeks New Life for Planar Transistors - IEEE Spectrum".

- ^ "The Increasingly Uneven Race to 3nm/2nm". 24 May 2021.

- ^ "What's Different About Next-Gen Transistors". 20 October 2022.

- ^ "Intel's Stacked Nanosheet Transistors Could be the Next Step in Moore's Law".

- ^ "Nanowire Transistors Could Keep Moore's Law Alive".

- ^ "Nanowires give vertical transistors a boost". 2 August 2012.

- ^ "Transistors will stop shrinking in 2021, but Moore's law will live on". 25 July 2016.

- ^ "7nm, 5nm, 3nm: The new materials and transistors that will take us to the limits of Moore's law | Extremetech". 26 July 2013.

- ^ "What's After FinFETs?". 24 July 2017.

- ^ "Transistor Options Beyond 3nm". 15 February 2018.

- ^ "Samsung, GF Ramp FD-SOI". 27 April 2018.

- ^ Shilov, Anton. "Samsung Completes Development of 5nm EUV Process Technology". AnandTech. Archived from the original on 2019-04-20. Retrieved 2019-05-31.

- ^ Cheng, Godfrey (14 August 2019). "Moore's Law is not Dead". TSMC Blog. TSMC. Retrieved 25 September 2023.

- ^ Schor, David (2019-04-06). "TSMC Starts 5-Nanometer Risk Production". WikiChip Fuse. Archived from the original on 2020-05-05. Retrieved 2019-04-07.

- ^ Shilov, Anton; Cutress, Ian. "GlobalFoundries Stops All 7nm Development: Opts To Focus on Specialized Processes". AnandTech. Archived from the original on 2019-10-12. Retrieved 2019-10-12.

- ^ Smith, Nicola; Liu, John (July 2021). "Taiwan chipmakers keep workers 'imprisoned' in factories to keep up with global pandemic demand". The Telegraph.

- ^ "Chip shortages lead to more counterfeit chips and devices". 14 June 2021.

- ^ Miller, Chris. "What are semiconductors, and why are they vital to the global economy?". World Economic Forum (Interview).

- ^ Whalen, Jeanne (June 14, 2021). "Countries lavish subsidies and perks on semiconductor manufacturers as a global chip war heats up". The Washington Post.

- ^ Shepardson, David (December 21, 2023). "China import concerns spur US to launch semiconductor supply chain review". Reuters.

- ^ Hille, Kathrin (3 November 2019). "US urges Taiwan to curb chip exports to China". Financial Times.

- ^ Allen, Gregory (November 26, 2024). "The True Impact of Allied Export Controls on the U.S. and Chinese Semiconductor Manufacturing Equipment Industries". Center for Strategic and International Studies.

- ^ Allen, Gregory (December 11, 2024). "Understanding the Biden Administration's Updated Export Controls". Center for Strategic and International Studies.

- ^ a b "VLSI Symposium - TSMC and Imec on Advanced Process and Devices Technology Toward 2nm". 25 February 2024.

- ^ "Power outage partially halts Toshiba Memory's chip plant". Reuters. June 21, 2019. Archived from the original on December 16, 2019. Retrieved December 16, 2019 – via www.reuters.com.

- ^ Labor, U. S. Dept of (February 19, 2000). Occupational Outlook Handbook. JIST Publishing. ISBN 978-1-56370-677-6 – via Google Books.

- ^ "Water Scarcity and the Semiconductor Industry". large.stanford.edu.

- ^ a b c "Introduction to Semiconductor Technology" (PDF) (application note). STMicroelectronics. AN900.

- ^ a b Reinhardt, Karen; Kern, Werner (March 16, 2018). Handbook of Silicon Wafer Cleaning Technology. William Andrew. p. 223. ISBN 978-0-323-51085-1. Retrieved 8 January 2024.

- ^ Natraj Narayanswami (1999). "A Theoretical Analysis of Wafer Cleaning Using a Cryogenic Aerosol". Journal of the Electrochemical Society. 146 (2): 767–774. Bibcode:1999JElS..146..767N. doi:10.1149/1.1391679. Retrieved 8 January 2024.

- ^ Hars, Adele (October 20, 2022). "Wafer Cleaning Becomes Key Challenge In Manufacturing 3D Structures". Semiconductor Engineering.

- ^ Hattori, Takeshi (September 30, 2009). Cleaning and Surface Conditioning Technology in Semiconductor Device Manufacturing 11. The Electrochemical Society. ISBN 978-1-56677-742-1 – via Google Books.

- ^ Handbook of Integrated Circuit Industry. Springer. 27 November 2023. ISBN 978-981-99-2836-1.

- ^ Reiter, Tamas; McCann, Michael; Connolly, James; Haughey, Sean (February 2022). "An Investigation of Edge Bead Removal Width Variability, Effects and Process Control in Photolithographic Manufacturing". IEEE Transactions on Semiconductor Manufacturing. 35 (1): 60–66. doi:10.1109/TSM.2021.3129770. S2CID 244560651.

- ^ a b c LaPedus, Mark (November 16, 2017). "What's Next For Atomic Layer Etch?". Semiconductor Engineering.

- ^ a b "Epitaxy".

- ^ Pelé, A-F. (29 March 2022). "Unlocking the Potential of Molecular Beam Epitaxy". AspenCore. Retrieved 8 January 2024.

- ^ Vogler, D. (19 November 2008). "Ion beam deposition goes 300mm with Aviza's new tool". Gold Flag Media. Retrieved 8 January 2024.

- ^ Ryu, Je Hyeok; Kim, Byoung Hoon; Yoon, Sung Jin (2017). "Characterization of thin carbonized photoresist layer and investigation of dry strip process through real-time monitored variable temperature control". 2017 28th Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC). pp. 102–106. doi:10.1109/ASMC.2017.7969207. ISBN 978-1-5090-5448-0.

- ^ Einspruch, Norman G.; Brown, Dale M. (December 1, 2014). Plasma Processing for VLSI. Academic Press. ISBN 978-1-4832-1775-8 – via Google Books.

- ^ Verhaverbeke, S.; Beaudry, C.; Boelen, P. (2004). Aqueous Single Pass Single Wafer AI/Via Cleaning. Electrochemical Society. pp. 23–26. ISBN 978-1-56677-411-6. Retrieved 8 January 2024.

- ^ "Laser Lift-Off(LLO) Ideal for high brightness vertical LED manufacturing - Press Release - DISCO Corporation". www.disco.co.jp. Archived from the original on 2019-06-14. Retrieved 2019-05-26.

- ^ "Product Information | Polishers - DISCO Corporation". www.disco.co.jp. Archived from the original on 2019-05-26. Retrieved 2019-05-26.

- ^ "Product Information | DBG / Package Singulation - DISCO Corporation". www.disco.co.jp. Archived from the original on 2019-05-16. Retrieved 2019-05-26.

- ^ "Plasma Dicing (Dice Before Grind) | Orbotech". www.orbotech.com.[permanent dead link]

- ^ "Electro Conductive Die Attach Film(Under Development) | Nitto". www.nitto.com. Archived from the original on 2019-05-26. Retrieved 2019-05-26.

- ^ "Die Attach Film Adhesives". www.henkel-adhesives.com. Archived from the original on 2019-05-26. Retrieved 2019-05-26.

- ^ "From a Slice of Crystal to an IC Wafer - CHM Revolution". www.computerhistory.org.

- ^ a b "Study into human particle shedding". www.cleanroomtechnology.com. Archived from the original on 2020-10-15. Retrieved 2020-10-14.

- ^ "The ASYST SMIF system - Integrated with the Tencor Surfscan 7200". Chip History. Archived from the original on 2020-10-16. Retrieved 2020-10-14.

- ^ Miller, Michael J. (February 15, 2018). "How a Chip Gets Made: Visiting GlobalFoundries". PCMag Asia. Retrieved November 23, 2023.

- ^ Microlithography: Science and Technology, Second Edition. CRC Press. 3 October 2018. ISBN 978-1-4200-5153-7.

- ^ "Wafer Cleaning Procedures; Photoresist or Resist Stripping; Removal of Films and Particulates". www.eesemi.com. Archived from the original on 2020-10-15. Retrieved 2020-10-14.

- ^ Sugawara, M. (May 28, 1998). Plasma Etching: Fundamentals and Applications. OUP Oxford. ISBN 978-0-19-159029-0 – via Google Books.

- ^ Nojiri, Kazuo (October 25, 2014). Dry Etching Technology for Semiconductors. Springer. ISBN 978-3-319-10295-5 – via Google Books.

- ^ Sugawara, M. (May 28, 1998). Plasma Etching: Fundamentals and Applications. OUP Oxford. ISBN 978-0-19-159029-0 – via Google Books.

- ^ Li, Jinmin; Wang, Junxi; Yi, Xiaoyan; Liu, Zhiqiang; Wei, Tongbo; Yan, Jianchang; Xue, Bin (August 31, 2020). III-Nitrides Light Emitting Diodes: Technology and Applications. Springer Nature. ISBN 978-981-15-7949-3 – via Google Books.

- ^ Powell, R. A. (December 2, 2012). Dry Etching for Microelectronics. Elsevier. ISBN 978-0-08-098358-5 – via Google Books.

- ^ Lienig, Jens; Scheible, Juergen (March 19, 2020). Fundamentals of Layout Design for Electronic Circuits. Springer Nature. ISBN 978-3-030-39284-0 – via Google Books.

- ^ Köhler, Michael (July 11, 2008). Etching in Microsystem Technology. John Wiley & Sons. ISBN 978-3-527-61379-3 – via Google Books.

- ^ LaPedus, Mark (March 21, 2022). "Highly Selective Etch Rolls Out For Next-Gen Chips". Semiconductor Engineering.

- ^ Franssila, Sami (28 January 2005). Introduction to Microfabrication. John Wiley & Sons. ISBN 978-0-470-02056-2.

- ^ "1954: Diffusion Process Developed for Transistors | the Silicon Engine | Computer History Museum".

- ^ Lian, Yaguang (10 October 2022). Semiconductor Microchips and Fabrication: A Practical Guide to Theory and Manufacturing. John Wiley & Sons. ISBN 978-1-119-86780-7.

- ^ Glavish, Hilton; Farley, Marvin. Review of Major Innovations in Beam Line Design (PDF). 2018 22nd International Conference on Ion Implantation Technology (IIT). doi:10.1109/IIT.2018.8807986.

- ^ Fair, Richard B. (January 1998). "History of Some Early Developments in Ion-Implantation Technology Leading to Silicon Transistor Manufacturing" (PDF). Proceedings of the IEEE. 86 (1): 111–137. doi:10.1109/5.658764. Archived from the original (PDF) on 2 September 2007. Retrieved 26 February 2024.

- ^ "Ion implantation in CMOS Technology: Machine Challenges". Ion Implantation and Synthesis of Materials. Springer. 2006. pp. 213–238. doi:10.1007/978-3-540-45298-0_15. ISBN 978-3-540-23674-0.

- ^ Virtual Metrology Technique for Semiconductor Manufacturing. The 2006 IEEE International Joint Conference on Neural Network Proceedings. doi:10.1109/IJCNN.2006.247284. S2CID 1194426.

- ^ "The Threat of Semiconductor Variability - IEEE Spectrum". IEEE.

- ^ Nishi, Yoshio; Doering, Robert (December 19, 2017). Handbook of Semiconductor Manufacturing Technology. CRC Press. ISBN 978-1-4200-1766-3 – via Google Books.

- ^ Grovenor, C. R. M. (October 5, 2017). Microelectronic Materials. Routledge. ISBN 978-1-351-43154-5 – via Google Books.

- ^ Semiconductor Manufacturing Technology. World Scientific Publishing Company. 3 March 2008. ISBN 978-981-310-671-0.

- ^ Nathan, Arokia; Saha, Samar K.; Todi, Ravi M. (August 2023). 75th Anniversary of the Transistor. John Wiley & Sons. ISBN 978-1-394-20244-7.

- ^ High-k/metal gates in leading edge silicon devices. 2012 SEMI Advanced Semiconductor Manufacturing Conference. doi:10.1109/ASMC.2012.6212925. S2CID 32122636.

- ^ Robertson, J., & Wallace, R. M. (2015). High-K materials and metal gates for CMOS applications. Materials Science and Engineering: R: Reports, 88, 1–41. doi:10.1016/j.mser.2014.11.001

- ^ Frank, M. M. (2011). High-k / metal gate innovations enabling continued CMOS scaling. 2011 Proceedings of the European Solid-State Device Research Conference (ESSDERC). doi:10.1109/essderc.2011.6044239

- ^ Gate-first high-k/metal gate DRAM technology for low power and high performance products. 2015 IEEE International Electron Devices Meeting (IEDM). doi:10.1109/IEDM.2015.7409775. S2CID 35956689.

- ^ "Integrating high-k /metal gates: gate-first or gate-last? | Semiconductor Digest".

- ^ "IEDM 2009: HKMG gate-first vs gate-last options | Semiconductor Digest".

- ^ "Tracing Samsung's Road to 14nm". 12 May 2015.

- ^ Complementary Metal Oxide Semiconductor. BoD – Books on Demand. August 2018. ISBN 978-1-78923-496-1.

- ^ LaPedus, Mark (July 24, 2017). "What's After FinFETs?". Semiconductor Engineering.

- ^ Tateshita, Y.; Wang, J.; Nagano, K.; Hirano, T.; Miyanami, Y.; Ikuta, T.; Kataoka, T.; Kikuchi, Y.; Yamaguchi, S.; Ando, T.; Tai, K.; Matsumoto, R.; Fujita, S.; Yamane, C.; Yamamoto, R.; Kanda, S.; Kugimiya, K.; Kimura, T.; Ohchi, T.; Yamamoto, Y.; Nagahama, Y.; Hagimoto, Y.; Wakabayashi, H.; Tagawa, Y.; Tsukamoto, M.; Iwamoto, H.; Saito, M.; Kadomura, S.; Nagashima, N. (2006). "High-Performance and Low-Power CMOS Device Technologies Featuring Metal/High-k Gate Stacks with Uniaxial Strained Silicon Channels on (100) and (110) Substrates". 2006 International Electron Devices Meeting. pp. 1–4. doi:10.1109/IEDM.2006.346959. ISBN 1-4244-0438-X. S2CID 23881959.

- ^ Narayanan, V. (2007). "High-k/Metal Gates- from research to reality". 2007 International Workshop on Physics of Semiconductor Devices. pp. 42–45. doi:10.1109/IWPSD.2007.4472451. ISBN 978-1-4244-1727-8. S2CID 25926459.

- ^ "The High-k Solution - IEEE Spectrum". IEEE.

- ^ Khare, Mukesh (2007). "High-K/Metal Gate Technology: A New Horizon". 2007 IEEE Custom Integrated Circuits Conference. pp. 417–420. doi:10.1109/CICC.2007.4405765. ISBN 978-1-4244-0786-6. S2CID 1589266.

- ^ Widmann, D.; Mader, H.; Friedrich, H. (9 March 2013). Technology of Integrated Circuits. Springer. ISBN 978-3-662-04160-4.

- ^ "BEOL Wiring Process for CMOS Logic".

- ^ a b c LaPedus, Mark (May 22, 2017). "The Race To 10/7nm". Semiconductor Engineering.

- ^ Chemical-Mechanical Planarization of Semiconductor Materials. Springer. 26 January 2004. ISBN 978-3-540-43181-7.

- ^ Copper Interconnect Technology. Springer. 22 January 2010. ISBN 978-1-4419-0076-0.

- ^ "Introduction to Copper / Low-K Interconnects & Electromigration Fundamentals".

- ^ Dubois, Geraud; Volksen, Willi (February 24, 2012). "Low- k Materials: Recent Advances". In Baklanov, Mikhail R.; Ho, Paul S.; Zschech, Ehrenfried (eds.). Low- k Materials: Recent Advances. Wiley. pp. 1–33. doi:10.1002/9781119963677.ch1. ISBN 978-0-470-66254-0 – via CrossRef.

- ^ Li, Z.; Tian, Y.; Teng, C.; Cao, H. (2020). "Recent Advances in Barrier Layer of Cu Interconnects". Materials. 13 (21): 5049. Bibcode:2020Mate...13.5049L. doi:10.3390/ma13215049. PMC 7664900. PMID 33182434.

- ^ "Ibm's Development of Copper Interconnect for Integrated Circuit".

- ^ "Cobalt Encapsulation Extends Copper to 10nm". 13 May 2014.

- ^ Löper, Philipp; Stuckelberger, Michael; Niesen, Bjoern; Werner, Jérémie; Filipič, Miha; Moon, Soo-Jin; Yum, Jun-Ho; Topič, Marko; De Wolf, Stefaan; Ballif, Christophe (2015). "Complex Refractive Index Spectra of CH3NH3PbI3 Perovskite Thin Films Determined by Spectroscopic Ellipsometry and Spectrophotometry". The Journal of Physical Chemistry Letters. 6 (1): 66–71. doi:10.1021/jz502471h. PMID 26263093. Retrieved 2021-11-16.

- ^ a b "Yield and Yield Management" (PDF). Cost Effective Integrated Circuit Manufacturing (PDF). Integrated Circuit Engineering Corporation. 1997. ISBN 1-877750-60-3. Archived from the original on 2023-01-22. Retrieved 2023-01-22.

{{cite book}}: CS1 maint: bot: original URL status unknown (link) - ^ Cutress, Dr Ian. "Early TSMC 5nm Test Chip Yields 80%, HVM Coming in H1 2020". AnandTech. Archived from the original on 2020-05-25. Retrieved 2020-04-12.

- ^ "Advanced MOSFETs and Novel Devices" (PDF). Archived from the original (PDF) on 2020-10-26. Retrieved 2020-10-23.

- ^ "Wafer Backgrind". eesemi.com. Archived from the original on 2021-01-22. Retrieved 2020-12-18.

- ^ "The post-fab process debate for 3D ICs: Foundry or OSATS". 30 April 2009.

- ^ "ATMPs: The Founding Stone of India's Semiconductor Era". 19 January 2022.

- ^ "U.S. Semiconductor Ecosystem Map". 20 March 2023.

- ^ Thadani, Akhil; Allen, Gregory C. (30 May 2023). "Mapping the Semiconductor Supply Chain: The Critical Role of the Indo-Pacific Region".

- ^ "Why tech pollution's going global". CNET. April 25, 2002. Retrieved February 17, 2024.

- ^ Baliga, B. (December 2, 2012). Epitaxial Silicon Technology. Elsevier. ISBN 978-0-323-15545-8 – via Google Books.

- ^ "Abating Potentially Dangerous Particles 2.5 µm and Smaller". 3 February 2020.

- ^ "Solid Scrubber for the Semiconductor Industry" (PDF). SBIR Success Stories. United States Environmental Protection Agency.

- ^ "Hi-tech without costing the Earth".

Further reading

[edit]- Kaeslin, Hubert (2008). Digital Integrated Circuit Design, from VLSI Architectures to CMOS Fabrication. Cambridge University Press., section 14.2.

- Wiki related to Chip Technology

- Yoshio, Nishi (2017). Handbook of Semiconductor Manufacturing Technology. CRC Press.

French

French Deutsch

Deutsch