ریزمعماری - ویکیپدیا، دانشنامهٔ آزاد

این مقاله نیازمند ویکیسازی است. لطفاً با توجه به راهنمای ویرایش و شیوهنامه، محتوای آن را بهبود بخشید. |

این مقاله نیازمند تمیزکاری است. لطفاً تا جای امکان آنرا از نظر املا، انشا، چیدمان و درستی بهتر کنید، سپس این برچسب را بردارید. محتویات این مقاله ممکن است غیر قابل اعتماد و نادرست یا جانبدارانه باشد یا قوانین حقوق پدیدآورندگان را نقض کرده باشد. |

در مهندسی کامپیوتر، ریز معماری یا همان سازماندهی کامپیوتر که گاهی به آن به صورت اختصار µarch یا uarch میگویند، شیوه ای است که از طریق آن یک معماری مجموعه دستورالعمل (ISA)، در یک پردازنده خاص پیادهسازی میشود.[۱] یک معماری مجموعه دستورالعمل، ممکن است از طریق ریز معماریهای متفاوتی پیادهسازی شود.[۲][۳]پیادهسازیها ممکن است به دلیل اهداف متفاوت از طراحی یا به دلیل تغییر تکنولوژی، تفاوت داشته باشند.[۴]

معماری کامپیوتر ترکیبی از ریز معماری و معماری مجموعه دستورالعمل است.

ارتباط با معماری مجموعه دستورالعمل

[ویرایش]معماری مجموعه دستورالعمل، تقریباً مشابه یک مدل برنامهنویسی برای یک پردازنده است، چنانکه توسط یک برنامهنویس زبان اسمبلی یا نویسندهٔ کامپایلر دیده میشود. معماری مجموعه دستورالعمل، حاوی مدل اجرا، ثباتهای پردازنده، فرمتهای آدرس و داده و … است. ریز معماری، حاوی اجزای تشکیل دهندهٔ پردازنده است و اینکه چگونه این اجزا به یکدیگر متصل میشوند و با هم همکاری میکنند تا ISA را پیادهسازی کنند.

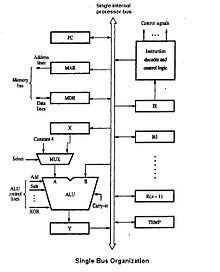

ریز معماری یک ماشین معمولاً به شکل دیاگرامهایی (با جزئیات زیاد یا کم) نشان داده میشود، که توصیف کننده ارتباطات بین عناصر مختلف ریز معماری ماشین است که ممکن است حاوی هر چیزی، از گیتهای منفرد و رجیسترها گرفته تا واحد محاسباتی و منطق (ALU) کامل و حتی عناصر بزرگتر باشد. این دیاگرامها بهطور کلی، مسیر داده (datapath، جایی که داده قرار داده میشود) و مسیر کنترل (که میتوان گفت داده را هدایت میکند) را از هم جدا میکنند.[۵]

فردی که یک سیستم را طراحی میکند، معمولاً ریز معماری خاصی را به شکل نوعی دیاگرام جریان داده رسم میکند. دیاگرام ریز معماری، شبیه یک دیاگرام بلاک، عناصر معماری از جمله مثلاً واحد محاسباتی و منطق و فایل رجیستری را به شکل یک سمبل شماتیک نشان میدهد. بهطور معمول این دیاگرام عناصر مذکور را به وسیله فلشها، خطوط ضخیم و خطوط باریک نشان میدهد تا موارد زیر را افتراق دهد: گذرگاههای سه وضعیتی (که نیازمند یک بافر سه-وضعیتی برای هر ابزاری است که از گذرگاه استفاده میکند)، گذرگاههای یک طرفه (همیشه توسط یک منبع استفاده میشود، مثلاً در کامپیوترهای ساده، که همیشه گذرگاه آدرس توسط رجیستر آدرس حافظه راه اندازی میشوند)، و خطوط کنترل منفرد. کامپیوترهای بسیار ساده دارای یک سازماندهی گذرگاه دادهٔ منفرد هستند- آنها دارای یک گذرگاه سه وضعیتی منفرد هستند. در دیاگرام کامپیوترهای پیچیدهتر معمولاً چندین گذرگاه سه وضعیتی وجود دارد که کمک میکند تا ماشین بتواند عملیات بیشتری را بهطور همزمان انجام دهد.

هر عنصر ریز معماری، توسط یک شماتیک نمایش داده میشود که توصیف کننده اتصالات بین دروازههای منطقی مورد استفاده برای پیادهسازی آن است. هر دروازه منطقی، توسط یک دیاگرام مدار نمایش داده میشود که توصیف کننده اتصالات ترانزیستورهای مورد استفاده برای پیادهسازی آن در خانوادهٔ منطقی خاصی است. ماشینهایی که دارای ریز معماری متفاوت هستند، ممکن است دارای ISA یکسان باشند، و بنابراین میتوانند برنامههای مشابهی را اجرا کنند. ریز معماریهای جدید و/یا راه حلهای مداربندی، همراه با پیشرفت در تولید نیمه رسانهها موجب شدهاست تا نسلهای جدید پردازندهها درحالی که از ISA مشابهی استفاده میکنند، به عملکردهای بالاتری دست یابند.

بهطور کلی، یک ریز معماری، میتواند به تنهایی چندین ISA مختلف را فقط با تغییرات کوچکی در ریزکد اجرا کند.

ویژگیها

[ویرایش]مسیر داده خط لوله (pipeline) شایعترین طراحی مسیر داده در معماریهای امروزی است. این تکنیک در اکثر ریزپردازندههای جدید، میکروکنترلرها و پردازندههای سیگنال دیجیتال استفاده میشود. معماری خط لوله ای امکان اجرای چندین دستورالعمل را بهصورت همپوشان فراهم میکند که بسیار شبیه یک خط سر همبندی است. خط لوله حاوی چندین مرحلهٔ متفاوت است که در طراحیهای ریز معماری اهمیت زیادی دارند. برخی از این مراحل عبارتند از: واکشی (fetch)، کدگشایی دستورالعمل (decoding)، اجرا (execution)، و نوشتن مجدد. برخی معماریها حاوی مراحل دیگری هستند از جمله، دسترسی به حافظه. طراحی خط لولهها یکی از مهمترین کارهای مربوط به ریز معماری است.

واحدهای اجرایی نیز اهمیت زیادی در ریز معماری دارند. واحدهای اجرایی عبارتند از: واحدهای محاسباتی و منطق (ALU) واحدهای ممیز شناور (FPU)، واحدهای بارگذاری/ذخیرهسازی (load/store)، پیشبینی انشعاب و SIMD. این واحدها عملیات یا محاسبات یک پردازنده را انجام میدهند. انتخاب تعداد واحدهای اجرایی، تأخیر آنها، و بازدهی آنها، یک بخش مهمی از طراحی در رابطه با ریز معماری است. اندازه تأخیر، بازدهی، و اتصالات حافظهها در داخل سیستم، نیز تصمیمهای مربوط به ریز معماری است.

تصمیمات طراحی سطح-سیستمی، من جمله اینکه آیا ابزارهای جانبی نظیر کنترلکنندههای حافظه هم باید اضافه شوند یا خیر، را میتوان بخشی از فرایند طراحی ریز معماری در نظر گرفت، که میتواند شامل تصمیماتی در رابطه با سطح عملکرد و اتصالات این ابزارهای جانبی باشد.

برخلاف طراحی معماری، که در آن دست یابی به یک سطح عملکرد خاص هدف اصلی است، طراحی ریز معماری توجه بیشتری به سایر محدودیتها دارد. از آنجایی که تصمیمات مربوط به طراحی ریز معماری، اثر مستقیمی بر این دارد که چه چیزی داخل سیستم میشود، لذا باید به مسائلی همچون مساحت/هزینهٔ چیپ، مصرف انرژی، پیچیدگی منطقی، سهولت اتصالات، قابلیت تولید، سهولت خطا زدایی و قابلیت تست شدن توجه کرد.

مفاهیم ریزمعماری

[ویرایش]چرخههای دستورالعمل

[ویرایش]تمام پردازندههای تک تراشه ای یا چند تراشهای برای اجرای برنامهها:

- یک دستورالعمل را میخوانند و آن را کدگشایی میکنند.

- دادهای را که برای پردازش دستورالعمل لازم است، پیدا میکنند.

- دستورالعمل را پردازش میکنند.

- نتایج را مینویسند.

این چرخهٔ دستورالعمل تا زمانی که کامپیوتر روشن است، تکرار میشود.

ریز معماری چند چرخه ای

[ویرایش]از نظر تاریخی، اولین کامپیوترها دارای طراحی چند چرخه ای بودند. معمولاً کوچکترین و ارزانترین کامپیوترها هنوز از این تکنیک استفاده میکنند. معماریهای چند چرخه ای معمولاً از کمترین تعداد عناصر منطقی و مقادیر قابل قبولی از انرژی استفاده میکنند. این معماریها را میتوان طوری طراحی کرد، تا دارای زمانبندی مشخص و اعتماد پذیری بالایی باشند. از آنجایی که آنها فاقد خط لوله هستند در نتیجه دچار معطلی به دلیل انشعابات شرطی یا وقفهها نمیشود. با این وجود، سایر ریز معماریها، معمولاً دستورالعملهای بیشتری به ازای واحد زمانی انجام میدهند و در عین حال از خانواده منطقی مشابهی استفاده میکنند. زمانی که در رابطه با بهبود عملکرد صحبت میکنیم، معمولاً منظور ما یک طراحی چند چرخه ای است.

در یک سیستم چند چرخه ای، کامپیوتر در طی چندین چرخهٔ ساعت، چهار مرحله را به ترتیب انجام میدهد. برخی طراحیها میتوانند توالی مذکور را، با کامل کردن مراحل پشت سرهم در لبههای ساعت، بهصورت یک در میان، در دو چرخهٔ ساعت انجام دهند. در این حالت، معمولاً عملیات طولانیتر در خارج از چرخه اصلی رخ میدهد. برای مثال، مرحله ۱ در لبه بالاروندهٔ اولین چرخه و مرحله ۲ در لبهٔ پایین روندهٔ اولین چرخه و به همین شکل ادامه پیدا میکند.

در منطق کنترل، ترکیبی از شمارندهٔ چرخه، وضعیت چرخه (بالا یا پایین)، و بیتهای رجیستر کدگشایی دستورالعمل، مشخص میکند که دقیقاً هر قسمت از کامپیوتر باید چه کاری انجام دهد. برای طراحی منطق کنترل میتوان جدولی از بیتها را ایجاد کرد که در هر چرخه از هر دستورالعمل، سیگنالهای کنترل به هر قسمت از کامپیوتر را مشخص میکند. سپس این جدول منطقی را میتوان در یک نرمافزار شبیهساز که کد تست را اجرا میکند، تست کرد. اگر این جدول منطقی، در یک حافظه قرار داده شود و به شکل واقعی برای به راه انداختن یک کامپیوتر واقعی استفاده شود، آنگاه به آن یک ریز برنامه گویند. در برخی طراحیهای کامپیوتری، این جدول منطقی به فرم منطق ترکیبی ساخته شده از گیتهای منطقی، بهینهسازی میشود که معمولاً این کار با استفاده از یک برنامه کامپیوتری که منطق را بهینهسازی میکند، انجام میشود. کامپیوترهای قدیمی از طراحی منطقی در موقع لزوم، برای کنترل استفاده میکردند تا زمانی که آقای Maurice Wilkes این روش جدولی را کشف کرد و آن را ریز برنامهنویسی نامید.[۶]

افزایش سرعت اجرا

[ویرایش]آنچه که این مجموعه مراحل به نظر ساده را پیچیده میکند، این حقیقت است که، سلسله مراتب حافظه که شامل: حافظه نهان، حافظه اصلی، و حافظه غیر فرار نظیر هارد دیسکها (جایی که دستورالعملها و دادهٔ برنامه قرار دارد) میشود، همیشه کندتر از خود پردازنده است. مرحله ۲، معمولاً موجب یک تأخیر طولانی (از چشمانداز پردازنده) میشود. این تأخیر طولانی، در واقع، مدت زمانی است که داده پس از طی گذرگاه کامپیوتر میرسد. تحقیقات زیادی در رابطه با طراحیهایی انجام شدهاست که بتواند این تاخیرها را به حداقل ممکن برساند. طی مدت سالیان، هدف اصلی این بود که دستورالعملهای زیادی را به صورت موازی اجرا کنند و بدین طریق، سرعت اجرای مؤثر یک برنامه را افزایش دهند. این تلاشها منجر به ساختارهای منطقی و مداری پیچیده شد. در ابتدا این ساختارها فقط قابل پیادهسازی روی رایانههای بزرگ یا ابررایانههای گرانقیمت و پیشرفته بود، که دلیل آن، میزان مدار بندی مورد نیاز برای آنها بود. با پیشرفت تولید نیمه هادیها، ساختارهای بیشتری از این دست قابل پیادهسازی روی یک چیپ نیمه هادی منفرد بود.

انتخاب مجموعه دستورالعمل

[ویرایش]طی سالیان، مجموعههای دستورالعمل، از انواع بسیار ساده در ابتدا تا انواع بسیار پیچیده (از جنبههای مختلف) تغییر پیدا کردهاست. در سالهای اخیر، معماریهای بارگیری/ذخیرهسازی، VLIW و انواع EPIC مرسوم بودهاند. معماریهایی که با موازی گرایی داده مرتبط هستند عبارتند از: SIMD و بردارها. برخی القاب که برای اشاره به کلاسهایی از معماریهای پردازنده استفاده میشوند، چندان توصیف کننده نیستند، خصوصاً برچسب CISC. بسیاری از طراحیهای ابتدایی که عطف به ماسبق CISC نامیده میشدند، در واقع، بهطور چشمگیری سادهتر از پردازندههای جدید RISC (از جنبههای مختلف) هستند.

با این وجود، انتخاب ISA ممکن است تأثیر زیادی روی پیچیدگی پیادهسازی ابزارهای با کارایی بالا داشته باشد. رویکرد اصلی که برای ساخت اولین پردازندههای RISC استفاده شد، این بود که دستورالعملها تا میزان حداقل پیچیدگی سمانتک منفرد ساده شوند و در عین حال، همراه با نظم کدگذاری و سادگی زیاد باشد. چون این دستورالعملهای یکدست، به شیوه خط لولهی و بهسادگی واکشی، کدگشایی، و اجرا میشدند، لذا یک رویکرد ساده برای کاهش تعداد سطوح منطقی با هدف دستیابی به فرکانسهای اجرایی بالا بود؛ حافظههای نهان دستورالعمل، موجب جبران فرکانسهای اجرایی بالا و تراکم کد پایین ذاتی شدند، در حالی که مجموعههای بزرگ رجیستر، برای کاهش دسترسیهای حافظه تا حداقل امکان استفاده میشدند.

خط لوله دستورالعمل

[ویرایش]یکی از ابتداییترین و قویترین تکنیکها برای بهبود عملکرد، استفاده از خط لوله دستورالعمل است. طراحیهای ابتدایی پردازنده قادر بودند تا تمام مراحل بالا را در یک دستورالعمل اجرا کنند و سپس به سراغ دستورالعمل بعدی بروند. بخشهای زیادی از مدار بندی در هر مرحله بلا استفاده میماند. برای مثال، ممکن بود مدار کدگشایی دستورالعمل، در طی اجرا بیکار بماند و ….

خط لوله میتواند عملکرد را بهبود بخشد، به این طریق که اجازه میدهد تا تعدادی دستورالعمل به صورت همزمان در پردازنده مشغول باشند. در همان مثال ابتدایی، پردازنده میتواند، در زمانی که مورد آخر منتظر نتایج است، یک دستورالعمل جدید را کد گشایی (مرحله ۱) کند. این وضعیت باعث میشود تا حداکثر ۴ دستورالعمل به صورت همزمان روی میز کار باشند، که باعث میشود، اینطور به نظر برسد که پردازنده، چهار برابر سریعتر است. اگرچه، هر دستورالعمل برای کامل شدن همچنان نیاز به همان مدت زمان قبلی دارد (کماکان چهار مرحله وجود دارد)، اما پردازشگر به صورت کلی، دستورالعملها را بسیار سریع تر کامل میکند.

معماری ریسک با جدا کردن هر مرحله از پردازش دستورالعمل بهصورت تر و تمیز، و یکسان کردن زمان پردازش هر کدام از آنها، موجب کوچکتر شدن و سادهتر شدن خط لوله میشود. پردازنده به شکلی شبیه یک مسیر سرهمبندی کار میکند. بدین صورت که دستورالعملها از یک طرف وارد میشوند و نتایج از طرف دیگر خارج میشوند. به دلیل کاهش پیچیدگی خط لوله مرسوم RISC، میتوان هستهٔ خط لولهٔ و حافظه نهان دستورالعملی را در یک دای به تنهایی جا داد. این دای در یک طراحی CISC، فقط میتواند هستهٔ مذکور را به تنهایی جا دهد. این وضعیت، دلیل حقیقی سریع تر بودن RISC است. طراحیهای ابتدایی نظیر، اسپارک و میپس معمولاً بیش از ۱۰ برابر سریع تر از روشهای CISC اینتل و موتورولا، با سرعت ساعت یکسان و هزینه یکسان، اجرا میشدند.

خط لولهها، به هیچ وجه، محدود به طراحیهای RISC نیستند. در سال ۱۹۸۶، بهترین پیادهسازی VAX، کهVAX 8800 نام داشت، نوعی طراحی با خط لوله بسیار زیاد بود که اندکی پیش از اولین طراحیهای تجاری میپس و اسپارک تولید شد. در حال حاضر، اکثر پردازندههای جدید (حتی پردازندههای نهفته) دارای خط لوله هستند. پردازندههای ریز کدگذاری شده و بدون خط لوله، فقط در پردازندههای نهفتهای که محدودیت بسیار زیادی از نظر مساحت دارند، دیده میشوند. ماشینهای CISC بزرگ، از VAX 8800 گرفته تا پنتیوم ۴ و Athlon جدید، هم با ریزکد و هم با خط لوله پیادهسازی شدهاند. بهبود در خط لوله و حافظه نهان، دو مزیت مهم ریز معماری بودند، که باعث شدند عملکرد پردازنده همزمان با پیشرفت تکنولوژی مداری که روی آن پیادهسازی میشوند، افزایش یابد.

حافظه نهان

[ویرایش]مدت زمان زیادی طول نکشید، قبل از اینکه پیشرفت در تولید چیپ، این امکان را فراهم آورد تا مداربندی حتی بیشتری روی دای قرار گیرد، و طراحان شروع به یافتن راه حلهایی برای استفاده از آن شدند. یکی از رایجترین اینها، اضافه کردن مقادیر فزایندهای از حافظه نهان (cache) روی دای بود. بهطور ساده میتوان گفت، حافظه نهان یک حافظه بسیار سریع است و قابل دسترسی در چند سیکل اندک میباشد، این در حالی است که دسترسی به حافظه اصلی نیاز به سیکلهای زیادی دارد. پردازنده دارای یک کنترل کنندهٔ حافظهٔ نهان است که خواندن و نوشتن در کش را به شکل خودکار درمیآورد. اگر دادهٔ مورد نظر در کش وجود داشته باشد، به سادگی نمایان میشود، در حالی که اگر وجود نداشته باشد، پردازنده معطل میماند تا زمانی که کنترل کنندهٔ حافظه نهان آن را به داخل خود بخواند.

طراحیهای RISC در اواسط تا اواخر دههٔ ۱۹۸۰ شروع به اضافه کردن حافظه نهان کردند، که معمولاً فقط ۴ کیلوبایت حجم داشت. این عدد در طی زمان افزایش یافت و پردازندههای معمول در حال حاضر دارای حداقل ۵۱۲ کیلوبایت حافظهٔ نهان هستند، و پردازندههای قوی تر دارای ۱، ۲، یا حتی ۴، ۶، ۸ یا ۱۲ مگابایت حافظهٔ نهان هستند که در سطوح مختلفی از سلسله مراتب حافظه، سازماندهی میشوند. در صحبت کلی، هر قدر مقدار کش بیشتر باشد، عملکرد بیشتر میشود که دلیل آن کاهش معطلی است.

حافظههای نهان و خط لولهها مکمل خوبی برای هم هستند. پیش از این، معنی زیادی نداشت که خط لوله ای درست کنیم که سریعتر از مدت تأخیر دسترسی به حافظهٔ خارج از چیپ باشد. بهکارگیری حافظه نهان روی چیپ، به این معنی بود که خط لوله میتوانست با سرعتی معادل با تأخیر دسترسی به حافظه نهان، که زمان بسیار کمتری است، اجرا شود. این وضعیت موجب شد تا فرکانسهای اجرایی پردازندهها با سرعت بسیار بیشتری از فرکانس اجرایی حافظهٔ خارج از چیپ، افزایش یابد.

پیشبینی انشعاب

[ویرایش]یک مانع در برابر دسترسی به عملکردهای بالاتر از طریق موازی سازی در سطح دستورالعمل، معطلیها و شستشوهای خط لوله به دلیل انشعابات است. بهطور معمول، به صورت تأخیری در خط لوله مشخص میشود که آیا یک انشعاب شرطی، عملی خواهد شد یا خیر؛ زیرا انشعابات شرطی بستگی به نتایجی دارند که از یک رجیستر میآیند. از زمانیکه کدگشای دستورالعمل پردازنده متوجه میشود که با یک دستورالعمل انشعاب شرطی مواجهه شدهاست، تا زمانیکه مقدار رجیستر تصمیم گیرنده، قابل خواندن میشود، خط لوله باید یا برای چندین چرخه معطل بماند، یا اینکه اگر نخواهد معطل بماند و انشعاب را انتخاب کند، آنگاه این امکان وجود دارد تا شسته شود. با افزایش سرعتهای ساعت، عمق خط لوله نیز افزایش مییابد و برخی پردازندههای جدید ممکن است دارای ۲۰ مرحله یا حتی بیشتر باشند. بهطور متوسط، در هر پنج اجرای دستورالعمل، یک انشعاب وجود دارد؛ بنابراین، بدون هرگونه مداخله ای دیگر، این مقدار، زمان زیادی از معطلی محسوب میشود.

تکنیکهایی نظیر پیشبینی انشعاب و اجرای حدسی، برای کاهش عوارض انشعاب استفاده میشوند. پیشبینی انشعاب به این معنی است که سختافزار بر اساس آموزههای قبلی، حدس میزند که آیا یک انشعاب خاص اجرا خواهد شد یا خیر. در واقعیت یک مسیر از انشعاب، در مقایسه با مسیر دیگر، بیشتر فراخوان میشود. طراحیهای جدید، دارای سیستمهای پیشبینی آماری پیچیدهتری هستند، که از نتایج پیشبینیهای قبلی، برای پیشبینی بعدی با دقت بیشتر استفاده میکنند. این حدسها باعث میشود تا، سختافزار بدون منتظر ماندن برای خواندن رجیستر، دستورالعملها را از پیش واکشی کند. اجرای حدسی، یک قدم فراتر است، به این شکل که، کدی که مربوط به مسیر پیشبینی شدهاست، نه تنها از پیش واکشی میشود، بلکه قبل از اینکه مشخص شود که آیا انشعاب مذکور باید اجرا شود یا خیر، اجرا نیز میشود. زمانی که حدس درست باشد، این روش منجر به عملکرد بهتر میشود، از سوی دیگر، زمانی که حدس غلط باشد منجر به خسارت زیادی میشود، زیرا دستورالعملها باید مجدداً انجام شوند.

ابراسکالر

[ویرایش]حتی با وجود تمام پیچیدگی و گیتهای اضافهٔ مورد نیاز برای پشتیبانی از مفاهیمی که ذکر شد، بهبود پیشرفتها در تولید نیمرسانا، به زودی باعث شد که حتی گیتهای منطقی بیشتری مورد استفاده قرار گیرد.

در چارچوب بالا، پردازنده بخشهایی از یک دستورالعمل را در هر لحظه اجرا میکند. اگر بتوان چندین دستورالعمل را بهطور همزمان پردازش کرد، آنگاه، برنامههای کامپیوتری میتوانند سریع تر اجرا شوند. این همان چیزی است که پردازندههای سوپراسکالر به آن دست یافتهاند، یعنی افزایش تعداد واحدهای عملکردی، مثلاً ALUها. افزایش تعداد واحدهای اجرایی، فقط زمانی امکانپذیر شد که مساحت دای در یک پردازنده با قابلیت اجرای یک دستورالعمل در هر چرخهٔ ساعت، دیگر فراتر از محدودیت تولید مطمئن نمیرفت. در اواخر دهه ۱۹۸۰، طراحیهای سوپراسکالر شروع به ورود به بازار کردند.

در طراحیهای جدید بهطور رایجی، دو واحد بارگذاری، یک واحد ذخیرهسازی (بسیاری از دستورالعملها نتیجهای برای ذخیره کردن ندارند)، دو یا بیش از دو واحد ریاضی اعداد صحیح، دو یا بیش از دو واحد ممیز شناور، و معمولاً نوع خاصی از یک واحد SIMD. منطق آغاز دستورالعمل، با خواندن تعداد بسیار زیادی از دستورالعملها از حافظه و انتقال آنها به واحدهای اجرایی مختلف که در آن لحظه بیکار هستند، پیچیدهتر شدهاست. در آخر، نتایج حاصله جمعآوری و مرتب میشوند.

اجرای خارج از نوبت

[ویرایش]اضافه کردن حافظههای نهان، باعث کاهش تعداد و مدت زمان معطلیها میشود، که دلیل آن کاهش زمان انتظار برای واکشی داده از سلسله مراتب حافظه است. اما این امر بهطور کامل موجب برطرف شدن این معطلیها نمیشود.

در طراحیهای ابتدایی، یک خطای حافظه نهان (به انگلیسی: cache miss) باعث میشد تا کنترل کنندهٔ کش، پردازنده را وادار به توقف و انتظار کند. البته ممکن است دستورالعملهای دیگری در برنامه وجود داشته باشند که دادهٔ آنها در آن لحظه، در کش موجود باشد. اجرای خارج از نوبت، این امکان را فراهم میکند که دستورالعملهای آماده در زمانی که یک دستورالعمل قبلی برای کش منتظر است، پردازش شود و سپس، نتایج حاصل را مرتب میکند و طوری به نظر میرسد که همه چیز به ترتیب برنامهنویسی شده اجرا شدهاست. این تکنیک همچنین برای پیشگیری از سایر معطلیهای ناشی از وابستگی عملوندها استفاده شد، مثلاً زمانی که یک دستورالعمل، منتظر نتیجهٔ حاصل از یک عملیات ممیز شناور طولانی یا منتظر سایر عملیات چند چرخه ای است.

تغییر نام رجیستر

[ویرایش]هدف از تکنیک موسوم به تغییر نام رجیستر این است که، از اجرای بیهودهٔ دستورالعملهای برنامه به شکل متوالی به دلیل استفادهٔ مجدد از همان رجیسترها توسط همان دستورالعملها اجتناب شود. فرض کنید که دو گروه از دستورالعملها داریم که از رجیستر مشابهی استفاده میکنند. یک مجموعه از دستورالعملها ابتدا اجرا میشوند و رجیستر را برای استفاده توسط مجموعهٔ دیگر آزاد میکنند، اما اگر مجموعه دیگر، به یک رجیستر مشابه دیگر اختصاص داده شده باشد، آنگاه هر دو مجموعهٔ دستورالعمل میتوانند به صورت موازی یا به صورت متوالی اجرا شوند.

چند فرایندی و چند ریسمانی

[ویرایش]رشد ناسازگاری بین فرکانسهای اجرایی پردازنده و زمانهای دسترسی به DRAM، مانعی بر سر راه معماران کامپیوتر شدهاست. هیچکدام از تکنیکهایی که از روش موازی گرایی در سطح دستورالعمل در داخل یک برنامه بهرهگیری میکنند، نمیتوانند مشکل معطلی طولانی مدت را که ناشی از زمان لازم برای واکشی داده از حافظه اصلی است برطرف کنند. علاوه بر این، تعداد زیاد ترانزیستورها و فرکانسهای اجرایی بالا که برای تکنیکهای موازی گرایی پیشرفته تر در سطح دستورالعمل لازم است، موجب ایجاد گرمای بیشتر میشود، که دیگر قابل خنک کردن با روشهای ارزان نیست. به این دلایل، نسلهای جدید کامپیوتر شروع به بهرهگیری از سطوح بالاتری از موازی گرایی کردند که خارج از یک برنامه منفرد یا ریسمان برنامه است. این روش را گاهی رایانش بازدهی مینامند. این ایده از بازار رایانههای بزرگ نشات گرفت که برای پردازشهای تراکنش آنلاین در آنها، نه تنها سرعت اجرای یک تراکنش اهمیت داشت، بلکه قابلیت پاسخ دهی به تعداد بسیار زیادی از تراکنشها هم اهمیت داشت. از آنجایی که عملیات مبتنی بر تراکنش، نظیر مسیریابی شبکه و خدمات دهی وبسایت، به میزان زیادی در دهه گذشته افزایش پیدا کردهاست، لذا، صنعت کامپیوتر مجدداً روی ظرفیت و مشکلات بازدهی متمرکز شدهاست.

یک روش برای دستیابی به این موازی گرایی، استفاده از سیستمهای چند پردازنده ای است، یعنی سیستمهای کامپیوتری که دارای چندین پردازنده هستند. سرورهای چند پردازنده ای کوچک-مقیاس (۲ تا ۸)، که زمانی فقط در رایانههای بزرگ و ابررایانهها وجود داشتند، هماکنون به وفور، در بازار کسب و کارهای کوچک وجود دارند. در شرکتهای بزرگ، چند پردازندههای بزرگ-مقیاس (۱۶ تا ۲۵۶) رایج هستند. حتی کامپیوترهای شخصی با چندین پردازنده، از دهه ۱۹۹۰، ظهور یافتند.

با کاهش بیشتر اندازه ترانزیستور که مرهون پیشرفت تکنولوژی نیمه هادی بودهاست، پردازندههای چند هسته ای که در آن چندین پردازنده روی یک چیپ سیلیکونی پیادهسازی میشوند، ظاهر شدند و در ابتدا در بازار چیپهای نهفته استفاده شدند، که در آن پردازندههای سادهتر و کوچکتر، این امکان را فراهم میآوردند تا تعداد زیادی را بتوان روی یک قطعه از سیلیکون پیادهسازی کرد. در سال ۲۰۰۵، فناوری نیمه هادی این امکان را فراهم آورد تا چیپهای پردازندههای رومیزی دوگانهٔ پیشرفته، در حجم بالایی تولید شوند. برخی طراحیها، نظیر UltraSPARC T1 از شرکت Sun Microsystems، به طراحیهای سادهتر (اسکالر، in-order) برگشتند تا بتوانند پردازندههای بیشتری را روی یک قطعه از سیلیکون جا دهند. تکنیک دیگری که اخیراً رایجتر شدهاست، چند ریسمانی است. در تکنیک چند ریسمانی، زمانی که پردازنده مجبور است تا دادهها را از حافظهٔ کند سیستم واکشی کند، به جای معطل ماندن برای رسیدن این داده، به سراغ برنامهٔ دیگر یا ریسمان دیگری میرود که آماده اجرا است. اگرچه این روش موجب افزایش سرعت یک برنامه/ریسمان خاص نمیشود، اما باعث افزایش بازدهی کلی سیستم، از طریق کاهش زمان بیکاری پردازنده میشود.

بهطور مفهومی، چند ریسمانی معادل است با تعویض زمینه در سطح سیستم عامل. تفاوت در این است که یک پردازندهٔ چند هسته ای میتواند یک تعویض ریسمان را در یک چرخهٔ پردازنده انجام دهد، در حالیکه یک تعویض زمینه، بهطور معمول نیازمند صدها یا هزاران چرخهٔ پردازنده است. این کار از طریق افزایش تعداد سختافزار وضعیت (مثلاً فایل رجیستر و شمارندهٔ برنامه) برای هر ریسمان فعال انجام میشود. ارتقای بیشتر در این زمینه از طریق چند ریسمانی همزمان انجام میشود. این تکنیک این امکان را فراهم میکند تا پردازندههای سوپر اسکالر، دستورالعملهایی را از چندین برنامه/ریسمان، بهطور همزمان در یک چرخه اجرا کنند.

منابع

[ویرایش]- ↑ Curriculum Guidelines for Undergraduate Degree Programs in Computer Engineering (PDF). Association for Computing Machinery. 2004. p. 60. Archived from the original (PDF) on 12 June 2019. Retrieved 14 April 2021.

Comments on Computer Architecture and Organization: Computer architecture is a key component of computer engineering and the practicing computer engineer should have a practical understanding of this topic...

- ↑ Murdocca, Miles; Heuring, Vincent (2007). Computer Architecture and Organization, An Integrated Approach. Wiley. pp. 151. ISBN 978-0-471-73388-1.

- ↑ Clements, Alan. Principles of Computer Hardware (4th ed.). pp. 1–2.

- ↑ Flynn, Michael J. (2007). "An Introduction to Architecture and Machines". Computer Architecture Pipelined and Parallel Processor Design. Jones and Bartlett. pp. 1–3. ISBN 978-0-86720-204-5.

- ↑ Hennessy, John L.; Patterson, David A. (2006). Computer Architecture: A Quantitative Approach (4th ed.). Morgan Kaufmann. ISBN 0-12-370490-1.

- ↑ Wilkes, M. V. (1969). "The Growth of Interest in Microprogramming: A Literature Survey". ACM Computing Surveys. 1 (3): 139–145. doi:10.1145/356551.356553. S2CID 10673679.

مشارکتکنندگان ویکیپدیا. «Microarchitecture». در دانشنامهٔ ویکیپدیای انگلیسی، بازبینیشده در ۱۱ آوریل ۲۰۲۱.

French

French Deutsch

Deutsch