اینتل ۸۰۸۷ - ویکیپدیا، دانشنامهٔ آزاد

Intel 8087 Math Coprocessor | |

| اطلاعات کلی | |

|---|---|

| راهاندازی | 1980 |

| عرضه | Intel, IBM[۱] |

| طراح | Intel |

| فروشندههای معمول | |

| Performance | |

| بیشترین نرخ کلاک CPU | 4 MHz به 10 MHz |

| معماری و طبقهبندی | |

| کوچکترین اندازهٔ عرضه شده | 3 μm |

| مجموعه دستورالعملها | x87 (coprocessor extension of x86-16) |

| ویژگیهای فیزیکی | |

| پکیجها |

|

| تاریخچه | |

| پیشین | 8231 |

| پسین | 80287 |

اینتل 8087، معرفی شده در سال 1980، اولین پردازنده عدد اعشاری x87 برای سری ریز پردازندههای 8086 بود.[۴][۵][۶]

هدف ۸۰۸۷ افزایش دادن سرعت محاسبات ریاضی عدد اعشاری، مانند جمع، تفریق، ضرب، تقسیم و ریشه مربع بود. ۸۰۸۷ همچنین توابع غیر جبری، مانند محاسبات نمایی، لگاریتمی یا مثلثاتی را محاسبه کرد، و علاوه بر عدد اعشاری، ۸۰۸۷ همچنین توانست بر روی اعداد صحیح دودویی بزرگ و اعداد صحیح دهدهی عمل کند. بسته به کاربرد خاص، بهبود عملکردی حدوداً از ۲۰ تا بیش از ۵۰۰ درصد، داشت. ۸۰۸۷ توانست حدود ۵۰۰۰۰ FLOPS[۵] را با استفاده از حدود ۲٫۴ وات انجام دهد.[۶] از نصب ۸۰۸۷ فقط عملیات ریاضی منتفع شدند؛ برای مثال، رایانههایی که کاربرد آنها پردازش متن بود، از هزینه اضافی (حدود ۱۵۰ دلار[۷]) و مصرف برق ۸۰۸۷ سودی نمیبردند.

۸۰۸۷ برای زمان خود یک IC پیشرفته بود، که محدودهٔ سیکل تولید تکنولوژی را جابهجا کرد. محصولات اولیه بسیار اندک بود.

فروش ۸۰۸۷ افزایش قابل ملاحظه ای داشت، زمانی که IBM یک سوکت پردازنده کمکی روی مادربرد IBM PC اضافه کرد. با توجه به کمبود تراشهها، آی بی ام ۸۰۸۷ را به عنوان یک گزینه برای PC ارائه نداد تا زمانی که شش ماه در بازار بود. توسعه ۸۰۸۷ منجر به استاندارد IEEE 754-1985 برای محاسبات عدد اعشاری شد. بعدها کمک-پردازندههای x87 برای پردازندههای ۸۰۱۸۶ (که در سازگاریهای PC استفاده نمیشد)، ۸۰۲۸۶، ۸۰۳۸۶ و 80386SX شدند. بعد از پردازشگر ۸۰۴۸۶، پردازنده Intel x86 دیگر از یک کمک-پردازندهٔ عدد اعشاری جداگانه استفاده نکردند؛ توابع عدد اعشاری با پردازنده یکپارچه شدند.

طراحی و توسعه

[ویرایش]اینتل قبل از این، واحد پردازنده محاسباتی ۸۲۳۱ و پردازنده عدد اعشاری ۸۲۳۲ تولید کرده بود. اینها برای استفاده با ۸۰۸۰ یا پردازندههای مشابه طراحی شده بود و به عنوان یک bus دادهای ۸ بیتی استفاده میشد. آنها به یک سیستم میزبان از طریق یک سیستم I/O برنامهریزی شده یا یک کنترلکننده DMA متصل میشدند.[۸]

۸۰۸۷ در ابتدا توسط بیل پولمن، مدیر مهندسی اینتل که به توسعه تراشه ۸۰۸۶ نظارت داشت، درک شد. بیل اقدامهای لازم را برای اطمینان از اینکه تراشه ۸۰۸۶ میتواند از یک تراشه ریاضی هنوز در حال توسعه پشتیبانی کند، انجام داد.

ولمن در سال ۱۹۷۷ برای طراحی تراشه ریاضی ۸۰۸۷ اقدام کرد. بروس راونال به عنوان معمار منسوب شد و جان پالمر به عنوان کمک-معمار و ریاضیدان برای این پروژه استخدام شد. این دو با یک طراحی انقلابی با ۶۴ بیت mantissa و ۱۶ بیت نما برای طولانیترین فرمت عدد حقیقی، با پردازندهٔ معماری پشتهای و ۸ ثبات پشته ۸۰ بیتی، با مجموعه ای از دستورالعملهای محاسباتی غنی آمدند. این طراحی چند مشکل عمده شناخته شده در محاسبات عددی و نرمافزار عددی را حل کرد: ایرادات خطای گرد کردن برای عملوندهای ۶۴ بیتی حذف شدند و تبدیلهای عددی برای تمام اعداد ۶۴ بیتی حل شد. پالمر نوشتههای ویلیام کاهان در مورد عدد اعشاری را عامل مؤثر قابل توجهی در طراحیشان نسبت داد.[۹]

طراحی ۸۰۸۷ در آغاز به دلیل طراحی جنجالی آن، در سانتا کلارا پذیرفته شد. در نهایت، این طراحی به اینتل اسرائیل نسبت داده شد، و رفی نوا یه عنوان راهنما پیادهسازی این تراشه انتخاب شد.

به پالمر، راونال و نوا حق امتیاز برای این طراحی اهدا شد.[۱۰] رابرت کوهلر و جان بیلیس نیز حق ثبت اختراع برای این تکنیک اعطا شد که در آن برخی از دستورالعملها با الگوی بیتی خاصی به کمک-پردازنده تخلیه شده بود.[۱۱]

۸۰۸۷ دارای ۴۵٬۰۰۰ ترانزیستور بود و به عنوان یک تخلیه بار ۳ میکرومتر مدار HMOS ساخته شده بود. آن در کنار ۸۰۸۶ یا ۸۰۸۸ کار کرد و حدود ۶۰ دستورالعمل جدید معرفی کرد. بیشتر ۸۰۸۷mnemonicهای اسمبلی با حرف F شروع میشوند مانند FADD FMUL , FCOM و … که باعث میشود از دستورالعملهای ۸۰۸۶ به راحتی قابل تشخیص باشند. رمزگذاری دودویی برای تمام دستورالعملهای ۸۰۸۷ با الگوی ۱۱۰۱۱های اعشاری، ۲۷ در مبنای ده، همان کاراکتر اسکی ESC اگر چه در مرتبه بالاتر بیت از یک بایت؛ پیشوندهای دستورالعملهای مشابه نیز گاهی به عنوان

"کدهای فرار" معرفی میشوند. دستور حفظی اختصاص داده شده توسط اینتل برای این کمک-پردازندهها دستورالعمل "ESC" است.

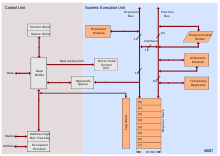

زمانی که پردازنده ۸۰۸۶ یا ۸۰۸۸ دستور ESC را اجرا میکرد، اگر بایت دوم (بایت ModR/M) یک عملوند حافظه را مشخص میکرد، پردازنده برای خواندن یک کلمه از حافظه مشخص شده در دستورالعمل (با استفاده از هر مد آدرسدهی) یک چرخه bus اجرا میکرد، ولی عملوند خوانده شده را در ثباتهای CPU ذخیره نمیکرد یا عملیاتی روی آن انجام نمیداد؛ 8087 bus را مشاهده و دستورالعملهای جریان همگام با ۸۰۸۶ را رمزگشایی میکرد، تشخیص دستورالعملهای کمک-پردازنده برای خودش ارزشمند بود. برای یک ۸۰۸۷ دستورالعمل با عملوند حافظه، اگر دستورالعمل فراخوانی شده برای عملوندی که خوانده شود، ۸۰۸۷ کلمهٔ داده خوانده شده توسط پردازنده اصلی را از اتوبوس داده میگیرد. اگر عملوند مقرر به خوانده شدن بلندتر از یک کلمه بود، ۸۰۸۷ نیز آدرس را از اتوبوس آدرس کپی خواهد کرد؛ سپس بعد از اتمام خواندن دادههای چرخه رانده شده توسط پردازنده، ۸۰۸۷ بلافاصله با استفاده از DMA کنترل اتوبوس را گرفته و بایتهای عملوند اضافی را خودش منتقل میکند. اگر یک دستورالعمل۸۰۸۷ با یک عملوند حافظه برای آن عملوندی که باید نوشته شود فراخوانی شود، ۸۰۸۷ کلمه خوانده شده از اتوبوس داده را در نظر نمیگیرد و فقط آدرس را کپی میکند، سپس از DMA درخواست میکند و کل عملوند را مینویسد، به همان طریقی که از انتهای یک عملوند گسترده شده میخواند. در این راه، پردازنده اصلی کنترل کلی اتوبوس و زمانبندی اتوبوس را در حالی که ۸۰۸۷ باقی زمینههای اجرای دستورالعملهای کمک-پردازنده را مدیریت میکند، حفظ میکند، بجز دورههای زمانی کوتاه DMA، زمانی که ۸۰۸۷ کنترل اتوبوس را برای خواندن یا نوشتن از یا در ثباتهای خود در دست میگیرد. به عنوان یک نتیجه از این طرح، ۸۰۸۷ تنها بر روی عملوندهایی که از حافظه یا از ثباتهای خودش گرفته بود میتوانست عمل کند، و هر تبادل اطلاعات بین ۸۰۸۷ و ۸۰۸۶ تنها از طریق RAM امکانپذیر بود.

برنامه اصلی پردازنده (CPU) در حالی که ۸۰۸۷ یک دستورالعمل را اجرا کردهاست، به اجرا ادامه میدهد؛ از منظر ۸۰۸۶ اصلی یا پردازنده ۸۰۸۸، یک دستورالعمل کمک-پردازنده به مدت پردازش opcode و هر چرخه عملوند حافظه (۲ چرخه ساعت برای بیعملوند، ۸ چرخه ساعت به علاوهٔ زمان محاسبه EA [پنج تا ۱۲ چرخه ساعت]، برای یک عملوند حافظه [به علاوهٔ ۴ چرخه ساعت بیشتر بر روی یک ۸۰۸۸]، برای انتقال دومین بایت از کلمه ،۸ بایت، عملوند)

زمان میگیرد، پس از آن که CPU دستورالعمل بعدی برنامه را اجرا کند.

بنابراین، یک سیستم با یک ۸۰۸۷ بهطور واقع توانایی پردازش موازی را داشت، اجرا کردن یک عملیات داخل ALU عدد صحیحِ پردازنده اصلی در حالی که در همان زمان یک عملیات عدد صحیح در کمک-پردازنده ۸۰۸۷ اجرا میشود.

از آنجایی که ۸۰۸۶ یا ۸۰۸۸ منحصراً جریان دستورالعملها وزمانبندی را کنترل میکردند و هیچ دسترسی مستقیمی به وضعیت داخلی ۸۰۸۷ ندارد، و به دلیل اینکه ۸۰۸۷ میتوانست یک دستور بر واحد زمان اجرا کند، برنامههای سیستمهای ۸۰۸۶/۸۰۸۷ یا ۸۰۸۸/۸۰۸۷ باید مطمئن میشدند که ۸۰۸۷ زمان کافی برای کامل اجرا کردن دستورالعمل قبلی مواجه شده را داشته باشد قبل از اینکه با دستور دیگری مواجه شود. دستورالعمل WAIT (برای پردازنده اصلی) برای این هدف درست شده بود، و اکثر اسمبلرها بهطور ضمنی قبل از بیشتر دستورها عدد اعشاری کمک-پردازندهها دستور WAIT را قرار میدهند. (در صورتی که برنامه از طرق دیگر اطمینان حاصل کند که زمان کافی بین اجرای دستورها ۸۰۸۷ حساس به زمان وجود دارد تا ۸۰۸۷ دستورالعمل دیگری قبل از اینکه دستور قبلی تمام شود دریافت نکند، دیگر لازم نیست قبل از اجرای یک دستور ۸۰۸۷ از دستور WAIT استفاده کرد. همچنین لزوماً به این شکل نیست که اگر WAIT به کار برده شد، بالافاصله به دستور ۸۰۸۷ بعدی برود) دستور WAIT منتظر پین ورودی -TEST 8086/8088 برای اعلام کردن میماند، و این پین به پین BUSY 8087 داخل تمام سیستمهایی که یک ۸۰۸۷ داشتند، متصل شده بود. (پس زمانی TEST اعلام میشود که BUSY از حالت اعلام شدن خارج شود).

به دلیل دستورالعمل پیش-فتچ شده صفهای ۸۰۸۶ و ۸۰۸۸ زمان مورد نیاز برای اجرای یک دستور تا اجرا شود همیشه با زمان لازم برای فتچ کردن یکسان نیست، یک کمک-پردازنده مثل ۸۰۸۷ نمیتواند بهتنهایی با دیدن bus تشخیص دهد که چه زمانی به دستورالعمل بعدی اجرا میشود. ۸۰۸۶ و ۸۰۸۸ دارای دو صف سیگنالهای وضعیت هستند که به کمک-پردازنده متصلند تا به آن امکان همگامسازی خود با زمانبندی داخلی CPU برای اجرای دستورالعملها از صف از پیش فتچ شده داشته باشد. ۸۰۸۷ صف از پیش فتچ شدهٔ خود را حفظ میکند، از جایی که آپکدهای کمک-پردازنده را میخواند و اجرا میکند. بهدلیل اینکه صفهای از پیش فتچ شده سایزهای متفاوت و الگوریتمهای متفاوت مدیریتی دارند، ۸۰۸۷ با مشاهده خاطهای معین bus پردازنده زمانی که سیستم ریسِت میشود، مشخص میکند که به چه نوع پردازندهای متصل شدهاست و بر این اساس صف دستورالعمل داخلی خود را تنظیم میکند. کپی کردن زائد صف پیش-فتچ شده سختافزار در CPU و کمک-پردازنده از جهت مصرف توان و از بین بردن فضای کلی ناکار آمد است، ولی باعث شد که رابط کمک-پردازنده به تعداد خیلی کمی پینهای IC اختصاص پیدا کند، که این مهم بود. در آن زمان که ۸۰۸۶، که رابط کمک-پردازنده را تعریف میکرد، معرفی شد ،ICهایی با بیش از ۴۰ پین کمیاب، گران بودند و مشکلاتی از قبیل ظرفیت اضافی lead ،که یک دلیل اصلی در محدود کردن سرعت سیگنال کردن بود، داشت.

کدهای عملیاتی کمک-پردازندهها به کدهایی از ۶ بیت تا ۲ بایت، شروع شده با توالی فرار رمزنگاری میشوند.

┐───────────┬───────────┌

│ 1xxx ۱۱۰۱ │ mmxx xrrr │

┘───────────┴───────────└

سه Xs اول، سه بیت اول آپکد عدد اعشاری هستند. سپس دوتا Ms، بعد از آن سه بیت آپکد عدد اعشاری نیمه دوم، دنبالش سه تا Rs هستند. Ms و Rs اطلاعات مد آدرسدهی را مشخص میکند.[۱۲]

برنامههای کاربردی باید نوشته میشدند تا از دستورالعمل خاص عدد اعشاری استفاده کنند. دز زمان اجرا، نرمافزار قادر بود تا کمک-پردازنده را برای عملیاتهای عدد اعشاری پیدا کند. زمانی که نمیتوانست پیدا کند، برای سازگاری عددی دقیق همان توابع عدد اعشاری میبایست داخل نرمافزار محاسبه شود یا تمام کمک-پردازنده در نرمافزار شبیهسازی شود.[۷]

ثباتها

[ویرایش]

خانوادهٔ x87 از سری ثباتهای قابل آدرسدهی مانند ثباتهای اصلی پردازندههای x86 بهطور مستقیم استفاده نمیکنند؛ جای آن، ثباتهای x87 یک ساختار پشتهای[۱۳] با ۸ سطح عمق که از st0 تا st7 سطحبندی میشوند، تشکیل میدهند. st0 بر روی پشته قرار دارد. عملیاتهای دستورالعملهای x87 با push کردن، محاسبه، و pop کردن مقادیر روی این پشته اجرا میشوند. اگرچه عملیاتهای دوتایی مثل FADD , FMUL ,FCMP و غیره ممکن است ضمناً از st0 و st1 یا st0 با یک حافظه یا یک ثبات بهطور غیر ضمنی استفاده کند؛ ثبات st0 میتواند به عنوان جمعکننده () استفاده شود و همچنین میتواند با هر یک از ۸ ثبات پشته از طریق فراخوانی دستورالعمل FXCH stX (کدهای D9C8..D9CFh) جابهجا شود. این موجب میشود که پشته x87 قابل استفاده به عنوان ۷ ثبات آزاد قابل آدرسدهی به علاوه یک جمعکننده شود. این مخصوصاً کارآمد بر روی پردازندههای x86 superescalar (پنتیوم ۱۹۹۳ و بعد از آن) است جایی که دستورالعمل تعویض به خطای صفر کلاک بهینهسازی شدهاند.

استاندارد عدد اعشاری IEEE

[ویرایش]هنگامی که اینتل ۸۰۸۷ را طراحی کرد، تصمیم گرفت که یک فرمت استاندارد عدد اعشاری برای طرحهای آینده درست کند. یک وجه مهم از لحاظ تاریخی این بود که به پایه استاندارد IEEE 754 تبدیل شد. ۸۰۸۷ همهٔ شروط مطرح شده در استاندارد IEEE 754 را پیادهساری نکرد، بهطوری که استاندارد تا ۱۹۸۵ به اتمام نرسید ولی ۸۰۳۸۷ به پایان رسید. ۸۰۸۷، دو نوع داده عدد اعشاری 32 / ۶۴ بیتی و یک فرمت موقت افزایشیافته ۸۰ بیتی (که در حافظه هم میتوانست ذخیره شود) برای ارتقا دقت در محاسبات پیچیده و بزرگ تأمین کرد. جدا از این ۸۰۸۷ یک فرمت پکشده BCD (دهدهی به رمز دودویی) ۸۰ بیتی/ ۱۸ رقمی و نوع دادههای ۱۶٬۳۲، و ۶۴ بیت عدد صحیح پیشنهاد داد.[۱۳]

| ۸۰۸۷ نوع داده | |||||||||||||||||

| 7 9 | . . . | 7 1 | . . . | 6 7 | . . . | 6 3 | . . . | 5 0 | . . . | 3 1 | . . . | 2 2 | . . . | 1 5 | . . . | 0 0 | (موقعیت بیتی) |

| ± | توان | کسر | ۸۰ بیت دقت افزوده واقعی | ||||||||||||||

| ± | توان | کسر | ۶۴ بیتی double-precision واقعی | ||||||||||||||

| ± | توان | کسر | ۳۲ بیت single-precision واقعی | ||||||||||||||

| ± | BCD Integer | عدد صحیح دهدهی ۱۸ رقمی | |||||||||||||||

| ± | صحیح | عدد صحیح دودویی ۶۴ بیتی | |||||||||||||||

| ± | صحیح | عدد صحیح باینری ۳۲ بیتی | |||||||||||||||

| ± | صحیح | عدد صحیح باینری ۱۶ بیتی | |||||||||||||||

بینهایت

[ویرایش]۸۰۸۷ مقادیر بینهایت را به صورت روش وابسته یا طرحی مدیریت میکند (از طریق وضعیت ثبات انتخاب میشود). در روش وابسته، با بینهایتهای مثبت و منفی به صورت دو مقدار متفاوت رفتار میشود. در روش طرحی، به عنوان نمایش بی علامتی برای اعداد بسیار کوچک یا بسیار بزرگ به کار برده میشود.[۱۴] این دو روش برخورد با بیتهایتدر نسخه پیشنویس استاندارد IEEE 754 گنجانده شدهاست. اگرچه، روش طرحی از نسخه رسمی IEEE 754 در سال ۱۹۸۵ برداشته شد. ۸۰۲۸۷ روش طرحی را به عنوان یک انتخاب حفظ کرد، اما ۸۰۳۸۷ و کمک-پردازندههای بعد از آن (شامل ۸۰۱۸۷) فقط روش وابسته را پشتیبانی میکردند.

واسط کمک-پردازنده

[ویرایش]۸۰۸۷ با کمک-پردازندههای بعدی متفاوت بود و آن اتصال مستقیم به busهای داده و آدرس بود. ۸۰۸۷ دنبال دستورالعملهایی که با توالی "۱۱۰۱۱" آغاز میشد میگشت و با آنها رفتار به خصوصی انجام میداد، به سرعت از پردازنده اصلی به DMA درخواست دسترسی اضطراری به عملوندهای حافظه بزرگتر از یک کلمه(۱۶ بیت) میداد، سپس بالافاصله کنترل bus را رها میکرد و یه پردازنده اصلی میداد. کمک-پردازنده تا زمانی که دستورالعمل کمک-پردازنده تمام نشده بود مانع اجرای برنامه نمیشد و برنامه باید دو پردازنده را با هم همگام کند، همانطور که بالا ذکر شد (در بخش «طراحی و توسعه»). یک پتانسیل کرش کردن وجود داشت اگر دستورالعمل کمک-پردازنده نتواند به کدی قابل فهم برای کمک-پردازنده دیکد کند. کمک-پردازندههای بعدی اینتل به این صورت به bus نمیشدند، ولی دستورالعملها را از طریق پردازنده اصلی با استفاده از پرتهای ورودی/خروجی.

این به خطای زمان اجرا منجر شد، ولی از پتانسیل کرش کردن جلوگیری شد زیرا پردازنده میتواست دستورالعملی که کمک-پردازنده نپذیرفته بود، را نادیده بگیرد.

۸۰۸۷ با استفاده از کنترل کردن bus حین ریست کردن چرخه، قادر بود تشخیص دهد که به یک ۸۰۸۸ متصل است یا به یک ۸۰۸۶.

۸۰۸۷ در تئوری قادر به همزمان کار کردن بود در هالی که ۸۰۸۶/۸۰۸۸ قادر به پردازش دستورالعملهای بیشتر بودند. در عمل، این احتمال وجود داشت که برنامه کار نکند اگر قبل از مواجه شدن با دستورالعمل بعدی، دستور قبلی کامل نشده باشد. اسمبلر بهطور اتوماتیک یک دستور 'FWAIT' بعد از هر آپکد کمک-پردازنده قرار میدهد و ۸۰۸۶/۸ را وادار به توقف اجرا میکند تا زمانی که ۸۰۸۷ سیگنال پایان بدهد[۱۵] این محدودیت در طرحهای بعدی برداشته شد.

مدلها و منابع دوم

[ویرایش]

کمک-پردازندههای اینتل ۸۰۸۷ در دو نوع ساخته شده بودند، یکی به صورت سرامیک پیچخورده DIP و یکی هم به DIP هرمی و طراحی شده بودند تا در بازه دمایی مقابل عمل کنند:

پسوندهای C,D،QD: صفر درجه سانتیگراد تا مثبت ۷۰ درجه سانتیگراد (مصرف تبلیغاتی)

پیشوندهای LC,LD,TC و TD: منفی ۴۰ درجه سیلسیوس تا مثبت ۸۵ درجه سیلسیوس (مصرف صنعتی)

پیشوندهای MC , MD: منفی ۵۵ درجه تا مثبت ۱۲۵ درجه (مصرف نظامی)

تمام مدلهای ۸۰۸۷ یک پک DIP چهل پینه داشتند و با ولتاژ ۵ ولت عمل میکرد، حدود ۲٫۴ وات مصرف میکرد. برخلاف کمک-پردازندههای بعد ۸۰۸۷ میبایست با همان سرعت clock پردازنده اصلی اجرا میکرد.[۱۶] پسوندهای قسمت عدد، سرعت clock را نشان میدهد:

| شماره مدل | فرکانس |

|---|---|

| اینتل ۸۰۸۷ | ۵ مگا هرتز |

| اینتل ۸۰۸۷–۱ | ۱۰ مگا هرتز |

| اینتل ۸۰۸۷–۲ | ۸ مگا هرتز |

| اینتل ۸۰۸۷–۳ | ۴ مگا هرتز |

| اینتل ۸۰۸۷–۶ | ۶ مگا هرتز |

- اصل 5 MHz اینتل C8087

- اصل 5 MHz اینتل D8087

- 8 MHz اینتل D8087-2

- اینتل 5 MHz C8087-۳

جانشین

[ویرایش]همانطور که پردازندههای ۸۰۸۸ و ۸۰۸۶ با قطعات بعدی جایگزین شدند، ۸۰۸۷ هم جایگزین شد. باقی کمک-پردازندههای اینتل ۸۰۲۸۷، ۸۰۳۸۷ و ۸۰۱۸۷ بودند.

از ۸۰۴۸۶ به بعد پردازندههای اینتل از کمک-پردازندههای عدد اعشاری جداگانه استفاده نمیکردند؛ عملاً همهشان، کمک-پردازندهها را در خودشان قرار داده بودند، بجز یک استثنای مهم که 80486SX، تغییر یافتهٔ 80486DX که FPU در آن غیرفعال شده بود. ۸۰۴۸۷ در واقع یک چیپ 80486DX با پین اضافی بود. هنگامی که نصب میشد پردازنده 80486SX را غیرفعال میکرد. پردازندههای 80486DX و Pentium و پردازندههای بعدی بر روی هسته پردازنده کارکرد عدد اعشاری داشتند.

مجموعه دستورالعمل FPU 8087

[ویرایش]مخففها:

- f32: تعداد ۳۲ بیت IEEE-754 عدد اعشاری

- f64: تعداد ۶۴ بیت IEEE-754 عدد اعشاری

- f80: تعداد ۸۰ بیت IEEE-754 عدد اعشاری

- i16: 16 عدد صحیح علامتدار

- i32: عدد صحیح علامتدار ۳۲ بیتی

- i64: 64 بیت عدد صحیح علامتدار

- bcd: 80 بیت عدد صحیح BCD علامتدار

- u16: وضعیت ۱۶ بیت یا کنترل کلمه

- env: وضعیت محیط FPU

- stt: حالت کامل FPU (محیط FPU + هشت ثبات ۸۰ بیت عدد اعشاری)

جدول شامل دستورالعمل کامل FPUهای ۸۰۸۷، ۸۰۲۸۷، ۸۰۳۸۷ و آخرین افزانه در FPUهای مبتنی بر Pentium است.

| Opcode | Mnemo | Opcode | Mnemo | Opcode | Mnemo | Opcode | Mnemo | Opcode | Mnemo | Opcode | Mnemo | Opcode | Mnemo | Opcode | Mnemo |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| D800 | FADD f32[BX+SI] | D808 | FMUL f32[BX+SI] | D810 | FCOM f32[BX+SI] | D818 | FCOMP f32[BX+SI] | D820 | FSUB f32[BX+SI] | D828 | FSUBR f32[BX+SI] | D830 | FDIV f32[BX+SI] | D838 | FDIVR f32[BX+SI] |

| D801 | FADD f32[BX+DI] | D809 | FMUL f32[BX+DI] | D811 | FCOM f32[BX+DI] | D819 | FCOMP f32[BX+DI] | D821 | FSUB f32[BX+DI] | D829 | FSUBR f32[BX+DI] | D831 | FDIV f32[BX+DI] | D839 | FDIVR f32[BX+DI] |

| D802 | FADD f32[BP+SI] | D80A | FMUL f32[BP+SI] | D812 | FCOM f32[BP+SI] | D81A | FCOMP f32[BP+SI] | D822 | FSUB f32[BP+SI] | D82A | FSUBR f32[BP+SI] | D832 | FDIV f32[BP+SI] | D83A | FDIVR f32[BP+SI] |

| D803 | FADD f32[BP+DI] | D80B | FMUL f32[BP+DI] | D813 | FCOM f32[BP+DI] | D81B | FCOMP f32[BP+DI] | D823 | FSUB f32[BP+DI] | D82B | FSUBR f32[BP+DI] | D833 | FDIV f32[BP+DI] | D83B | FDIVR f32[BP+DI] |

| D804 | FADD f32[SI] | D80C | FMUL f32[SI] | D814 | FCOM f32[SI] | D81C | FCOMP f32[SI] | D824 | FSUB f32[SI] | D82C | FSUBR f32[SI] | D834 | FDIV f32[SI] | D83C | FDIVR f32[SI] |

| D805 | FADD f32[DI] | D80D | FMUL f32[DI] | D815 | FCOM f32[DI] | D81D | FCOMP f32[DI] | D825 | FSUB f32[DI] | D82D | FSUBR f32[DI] | D835 | FDIV f32[DI] | D83D | FDIVR f32[DI] |

| D806nn | FADD f32[nn] | D80Enn | FMUL f32[nn] | D816nn | FCOM f32[nn] | D81Enn | FCOMP f32[nn] | D826nn | FSUB f32[nn] | D82Enn | FSUBR f32[nn] | D836nn | FDIV f32[nn] | D83Enn | FDIVR f32[nn] |

| D807 | FADD f32[BX] | D80F | FMUL f32[BX] | D817 | FCOM f32[BX] | D81F | FCOMP f32[BX] | D827 | FSUB f32[BX] | D82F | FSUBR f32[BX] | D837 | FDIV f32[BX] | D83F | FDIVR f32[BX] |

| D840n | FADD f32[BX+SI+n] | D848n | FMUL f32[BX+SI+n] | D850n | FCOM f32[BX+SI+n] | D858n | FCOMP f32[BX+SI+n] | D860n | FSUB f32[BX+SI+n] | D868n | FSUBR f32[BX+SI+n] | D870n | FDIV f32[BX+SI+n] | D878n | FDIVR f32[BX+SI+n] |

| D841n | FADD f32[BX+DI+n] | D849n | FMUL f32[BX+DI+n] | D851n | FCOM f32[BX+DI+n] | D859n | FCOMP f32[BX+DI+n] | D861n | FSUB f32[BX+DI+n] | D869n | FSUBR f32[BX+DI+n] | D871n | FDIV f32[BX+DI+n] | D879n | FDIVR f32[BX+DI+n] |

| D842n | FADD f32[BP+SI+n] | D84An | FMUL f32[BP+SI+n] | D852n | FCOM f32[BP+SI+n] | D85An | FCOMP f32[BP+SI+n] | D862n | FSUB f32[BP+SI+n] | D86An | FSUBR f32[BP+SI+n] | D872n | FDIV f32[BP+SI+n] | D87An | FDIVR f32[BP+SI+n] |

| D843n | FADD f32[BP+DI+n] | D84Bn | FMUL f32[BP+DI+n] | D853n | FCOM f32[BP+DI+n] | D85Bn | FCOMP f32[BP+DI+n] | D863n | FSUB f32[BP+DI+n] | D86Bn | FSUBR f32[BP+DI+n] | D873n | FDIV f32[BP+DI+n] | D87Bn | FDIVR f32[BP+DI+n] |

| D844n | FADD f32[SI+n] | D84Cn | FMUL f32[SI+n] | D854n | FCOM f32[SI+n] | D85Cn | FCOMP f32[SI+n] | D864n | FSUB f32[SI+n] | D86Cn | FSUBR f32[SI+n] | D874n | FDIV f32[SI+n] | D87Cn | FDIVR f32[SI+n] |

| D845n | FADD f32[DI+n] | D84Dn | FMUL f32[DI+n] | D855n | FCOM f32[DI+n] | D85Dn | FCOMP f32[DI+n] | D865n | FSUB f32[DI+n] | D86Dn | FSUBR f32[DI+n] | D875n | FDIV f32[DI+n] | D87Dn | FDIVR f32[DI+n] |

| D846n | FADD f32[BP+n] | D84En | FMUL f32[BP+n] | D856n | FCOM f32[BP+n] | D85En | FCOMP f32[BP+n] | D866n | FSUB f32[BP+n] | D86En | FSUBR f32[BP+n] | D876n | FDIV f32[BP+n] | D87En | FDIVR f32[BP+n] |

| D847n | FADD f32[BX+n] | D84Fn | FMUL f32[BX+n] | D857n | FCOM f32[BX+n] | D85Fn | FCOMP f32[BX+n] | D867n | FSUB f32[BX+n] | D86Fn | FSUBR f32[BX+n] | D877n | FDIV f32[BX+n] | D87Fn | FDIVR f32[BX+n] |

| D880nn | FADD f32[BX+SI+nn] | D888nn | FMUL f32[BX+SI+nn] | D890nn | FCOM f32[BX+SI+nn] | D898nn | FCOMP f32[BX+SI+nn] | D8A0nn | FSUB f32[BX+SI+nn] | D8A8nn | FSUBR f32[BX+SI+nn] | D8B0nn | FDIV f32[BX+SI+nn] | D8B8nn | FDIVR f32[BX+SI+nn] |

| D881nn | FADD f32[BX+DI+nn] | D889nn | FMUL f32[BX+DI+nn] | D891nn | FCOM f32[BX+DI+nn] | D899nn | FCOMP f32[BX+DI+nn] | D8A1nn | FSUB f32[BX+DI+nn] | D8A9nn | FSUBR f32[BX+DI+nn] | D8B1nn | FDIV f32[BX+DI+nn] | D8B9nn | FDIVR f32[BX+DI+nn] |

| D882nn | FADD f32[BP+SI+nn] | D88Ann | FMUL f32[BP+SI+nn] | D892nn | FCOM f32[BP+SI+nn] | D89Ann | FCOMP f32[BP+SI+nn] | D8A2nn | FSUB f32[BP+SI+nn] | D8AAnn | FSUBR f32[BP+SI+nn] | D8B2nn | FDIV f32[BP+SI+nn] | D8BAnn | FDIVR f32[BP+SI+nn] |

| D883nn | FADD f32[BP+DI+nn] | D88Bnn | FMUL f32[BP+DI+nn] | D893nn | FCOM f32[BP+DI+nn] | D89Bnn | FCOMP f32[BP+DI+nn] | D8A3nn | FSUB f32[BP+DI+nn] | D8ABnn | FSUBR f32[BP+DI+nn] | D8B3nn | FDIV f32[BP+DI+nn] | D8BBnn | FDIVR f32[BP+DI+nn] |

| D884nn | FADD f32[SI+nn] | D88Cnn | FMUL f32[SI+nn] | D894nn | FCOM f32[SI+nn] | D89Cnn | FCOMP f32[SI+nn] | D8A4nn | FSUB f32[SI+nn] | D8ACnn | FSUBR f32[SI+nn] | D8B4nn | FDIV f32[SI+nn] | D8BCnn | FDIVR f32[SI+nn] |

| D885nn | FADD f32[DI+nn] | D88Dnn | FMUL f32[DI+nn] | D895nn | FCOM f32[DI+nn] | D89Dnn | FCOMP f32[DI+nn] | D8A5nn | FSUB f32[DI+nn] | D8ADnn | FSUBR f32[DI+nn] | D8B5nn | FDIV f32[DI+nn] | D8BDnn | FDIVR f32[DI+nn] |

| D886nn | FADD f32[BP+nn] | D88Enn | FMUL f32[BP+nn] | D896nn | FCOM f32[BP+nn] | D89Enn | FCOMP f32[BP+nn] | D8A6nn | FSUB f32[BP+nn] | D8AEnn | FSUBR f32[BP+nn] | D8B6nn | FDIV f32[BP+nn] | D8BEnn | FDIVR f32[BP+nn] |

| D887nn | FADD f32[BX+nn] | D88Fnn | FMUL f32[BX+nn] | D897nn | FCOM f32[BX+nn] | D89Fnn | FCOMP f32[BX+nn] | D8A7nn | FSUB f32[BX+nn] | D8AFnn | FSUBR f32[BX+nn] | D8B7nn | FDIV f32[BX+nn] | D8BFnn | FDIVR f32[BX+nn] |

| DC00 | FADD f64[BX+SI] | DC08 | FMUL f64[BX+SI] | DC10 | FCOM f64[BX+SI] | DC18 | FCOMP f64[BX+SI] | DC20 | FSUB f64[BX+SI] | DC28 | FSUBR f64[BX+SI] | DC30 | FDIV f64[BX+SI] | DC38 | FDIVR f64[BX+SI] |

| DC01 | FADD f64[BX+DI] | DC09 | FMUL f64[BX+DI] | DC11 | FCOM f64[BX+DI] | DC19 | FCOMP f64[BX+DI] | DC21 | FSUB f64[BX+DI] | DC29 | FSUBR f64[BX+DI] | DC31 | FDIV f64[BX+DI] | DC39 | FDIVR f64[BX+DI] |

| DC02 | FADD f64[BP+SI] | DC0A | FMUL f64[BP+SI] | DC12 | FCOM f64[BP+SI] | DC1A | FCOMP f64[BP+SI] | DC22 | FSUB f64[BP+SI] | DC2A | FSUBR f64[BP+SI] | DC32 | FDIV f64[BP+SI] | DC3A | FDIVR f64[BP+SI] |

| DC03 | FADD f64[BP+DI] | DC0B | FMUL f64[BP+DI] | DC13 | FCOM f64[BP+DI] | DC1B | FCOMP f64[BP+DI] | DC23 | FSUB f64[BP+DI] | DC2B | FSUBR f64[BP+DI] | DC33 | FDIV f64[BP+DI] | DC3B | FDIVR f64[BP+DI] |

| DC04 | FADD f64[SI] | DC0C | FMUL f64[SI] | DC14 | FCOM f64[SI] | DC1C | FCOMP f64[SI] | DC24 | FSUB f64[SI] | DC2C | FSUBR f64[SI] | DC34 | FDIV f64[SI] | DC3C | FDIVR f64[SI] |

| DC05 | FADD f64[DI] | DC0D | FMUL f64[DI] | DC15 | FCOM f64[DI] | DC1D | FCOMP f64[DI] | DC25 | FSUB f64[DI] | DC2D | FSUBR f64[DI] | DC35 | FDIV f64[DI] | DC3D | FDIVR f64[DI] |

| DC06nn | FADD f64[nn] | DC0Enn | FMUL f64[nn] | DC16nn | FCOM f64[nn] | DC1Enn | FCOMP f64[nn] | DC26nn | FSUB f64[nn] | DC2Enn | FSUBR f64[nn] | DC36nn | FDIV f64[nn] | DC3Enn | FDIVR f64[nn] |

| DC07 | FADD f64[BX] | DC0F | FMUL f64[BX] | DC17 | FCOM f64[BX] | DC1F | FCOMP f64[BX] | DC27 | FSUB f64[BX] | DC2F | FSUBR f64[BX] | DC37 | FDIV f64[BX] | DC3F | FDIVR f64[BX] |

| DC40n | FADD f64[BX+SI+n] | DC48n | FMUL f64[BX+SI+n] | DC50n | FCOM f64[BX+SI+n] | DC58n | FCOMP f64[BX+SI+n] | DC60n | FSUB f64[BX+SI+n] | DC68n | FSUBR f64[BX+SI+n] | DC70n | FDIV f64[BX+SI+n] | DC78n | FDIVR f64[BX+SI+n] |

| DC41n | FADD f64[BX+DI+n] | DC49n | FMUL f64[BX+DI+n] | DC51n | FCOM f64[BX+DI+n] | DC59n | FCOMP f64[BX+DI+n] | DC61n | FSUB f64[BX+DI+n] | DC69n | FSUBR f64[BX+DI+n] | DC71n | FDIV f64[BX+DI+n] | DC79n | FDIVR f64[BX+DI+n] |

| DC42n | FADD f64[BP+SI+n] | DC4An | FMUL f64[BP+SI+n] | DC52n | FCOM f64[BP+SI+n] | DC5An | FCOMP f64[BP+SI+n] | DC62n | FSUB f64[BP+SI+n] | DC6An | FSUBR f64[BP+SI+n] | DC72n | FDIV f64[BP+SI+n] | DC7An | FDIVR f64[BP+SI+n] |

| DC43n | FADD f64[BP+DI+n] | DC4Bn | FMUL f64[BP+DI+n] | DC53n | FCOM f64[BP+DI+n] | DC5Bn | FCOMP f64[BP+DI+n] | DC63n | FSUB f64[BP+DI+n] | DC6Bn | FSUBR f64[BP+DI+n] | DC73n | FDIV f64[BP+DI+n] | DC7Bn | FDIVR f64[BP+DI+n] |

| DC44n | FADD f64[SI+n] | DC4Cn | FMUL f64[SI+n] | DC54n | FCOM f64[SI+n] | DC5Cn | FCOMP f64[SI+n] | DC64n | FSUB f64[SI+n] | DC6Cn | FSUBR f64[SI+n] | DC74n | FDIV f64[SI+n] | DC7Cn | FDIVR f64[SI+n] |

| DC45n | FADD f64[DI+n] | DC4Dn | FMUL f64[DI+n] | DC55n | FCOM f64[DI+n] | DC5Dn | FCOMP f64[DI+n] | DC65n | FSUB f64[DI+n] | DC6Dn | FSUBR f64[DI+n] | DC75n | FDIV f64[DI+n] | DC7Dn | FDIVR f64[DI+n] |

| DC46n | FADD f64[BP+n] | DC4En | FMUL f64[BP+n] | DC56n | FCOM f64[BP+n] | DC5En | FCOMP f64[BP+n] | DC66n | FSUB f64[BP+n] | DC6En | FSUBR f64[BP+n] | DC76n | FDIV f64[BP+n] | DC7En | FDIVR f64[BP+n] |

| DC47n | FADD f64[BX+n] | DC4Fn | FMUL f64[BX+n] | DC57n | FCOM f64[BX+n] | DC5Fn | FCOMP f64[BX+n] | DC67n | FSUB f64[BX+n] | DC6Fn | FSUBR f64[BX+n] | DC77n | FDIV f64[BX+n] | DC7Fn | FDIVR f64[BX+n] |

| DC80nn | FADD f64[BX+SI+nn] | DC88nn | FMUL f64[BX+SI+nn] | DC90nn | FCOM f64[BX+SI+nn] | DC98nn | FCOMP f64[BX+SI+nn] | DCA0nn | FSUB f64[BX+SI+nn] | DCA8nn | FSUBR f64[BX+SI+nn] | DCB0nn | FDIV f64[BX+SI+nn] | DCB8nn | FDIVR f64[BX+SI+nn] |

| DC81nn | FADD f64[BX+DI+nn] | DC89nn | FMUL f64[BX+DI+nn] | DC91nn | FCOM f64[BX+DI+nn] | DC99nn | FCOMP f64[BX+DI+nn] | DCA1nn | FSUB f64[BX+DI+nn] | DCA9nn | FSUBR f64[BX+DI+nn] | DCB1nn | FDIV f64[BX+DI+nn] | DCB9nn | FDIVR f64[BX+DI+nn] |

| DC82nn | FADD f64[BP+SI+nn] | DC8Ann | FMUL f64[BP+SI+nn] | DC92nn | FCOM f64[BP+SI+nn] | DC9Ann | FCOMP f64[BP+SI+nn] | DCA2nn | FSUB f64[BP+SI+nn] | DCAAnn | FSUBR f64[BP+SI+nn] | DCB2nn | FDIV f64[BP+SI+nn] | DCBAnn | FDIVR f64[BP+SI+nn] |

| DC83nn | FADD f64[BP+DI+nn] | DC8Bnn | FMUL f64[BP+DI+nn] | DC93nn | FCOM f64[BP+DI+nn] | DC9Bnn | FCOMP f64[BP+DI+nn] | DCA3nn | FSUB f64[BP+DI+nn] | DCABnn | FSUBR f64[BP+DI+nn] | DCB3nn | FDIV f64[BP+DI+nn] | DCBBnn | FDIVR f64[BP+DI+nn] |

| DC84nn | FADD f64[SI+nn] | DC8Cnn | FMUL f64[SI+nn] | DC94nn | FCOM f64[SI+nn] | DC9Cnn | FCOMP f64[SI+nn] | DCA4nn | FSUB f64[SI+nn] | DCACnn | FSUBR f64[SI+nn] | DCB4nn | FDIV f64[SI+nn] | DCBCnn | FDIVR f64[SI+nn] |

| DC85nn | FADD f64[DI+nn] | DC8Dnn | FMUL f64[DI+nn] | DC95nn | FCOM f64[DI+nn] | DC9Dnn | FCOMP f64[DI+nn] | DCA5nn | FSUB f64[DI+nn] | DCADnn | FSUBR f64[DI+nn] | DCB5nn | FDIV f64[DI+nn] | DCBDnn | FDIVR f64[DI+nn] |

| DC86nn | FADD f64[BP+nn] | DC8Enn | FMUL f64[BP+nn] | DC96nn | FCOM f64[BP+nn] | DC9Enn | FCOMP f64[BP+nn] | DCA6nn | FSUB f64[BP+nn] | DCAEnn | FSUBR f64[BP+nn] | DCB6nn | FDIV f64[BP+nn] | DCBEnn | FDIVR f64[BP+nn] |

| DC87nn | FADD f64[BX+nn] | DC8Fnn | FMUL f64[BX+nn] | DC97nn | FCOM f64[BX+nn] | DC9Fnn | FCOMP f64[BX+nn] | DCA7nn | FSUB f64[BX+nn] | DCAFnn | FSUBR f64[BX+nn] | DCB7nn | FDIV f64[BX+nn] | DCBFnn | FDIVR f64[BX+nn] |

| DE00 | FIADD i16[BX+SI] | DE08 | FIMUL i16[BX+SI] | DE10 | FICOM i16[BX+SI] | DE18 | FICOMP i16[BX+SI] | DE20 | FISUB i16[BX+SI] | DE28 | FISUBR i16[BX+SI] | DE30 | FIDIV i16[BX+SI] | DE38 | FIDIVR i16[BX+SI] |

| DE01 | FIADD i16[BX+DI] | DE09 | FIMUL i16[BX+DI] | DE11 | FICOM i16[BX+DI] | DE19 | FICOMP i16[BX+DI] | DE21 | FISUB i16[BX+DI] | DE29 | FISUBR i16[BX+DI] | DE31 | FIDIV i16[BX+DI] | DE39 | FIDIVR i16[BX+DI] |

| DE02 | FIADD i16[BP+SI] | DE0A | FIMUL i16[BP+SI] | DE12 | FICOM i16[BP+SI] | DE1A | FICOMP i16[BP+SI] | DE22 | FISUB i16[BP+SI] | DE2A | FISUBR i16[BP+SI] | DE32 | FIDIV i16[BP+SI] | DE3A | FIDIVR i16[BP+SI] |

| DE03 | FIADD i16[BP+DI] | DE0B | FIMUL i16[BP+DI] | DE13 | FICOM i16[BP+DI] | DE1B | FICOMP i16[BP+DI] | DE23 | FISUB i16[BP+DI] | DE2B | FISUBR i16[BP+DI] | DE33 | FIDIV i16[BP+DI] | DE3B | FIDIVR i16[BP+DI] |

| DE04 | FIADD i16[SI] | DE0C | FIMUL i16[SI] | DE14 | FICOM i16[SI] | DE1C | FICOMP i16[SI] | DE24 | FISUB i16[SI] | DE2C | FISUBR i16[SI] | DE34 | FIDIV i16[SI] | DE3C | FIDIVR i16[SI] |

| DE05 | FIADD i16[DI] | DE0D | FIMUL i16[DI] | DE15 | FICOM i16[DI] | DE1D | FICOMP i16[DI] | DE25 | FISUB i16[DI] | DE2D | FISUBR i16[DI] | DE35 | FIDIV i16[DI] | DE3D | FIDIVR i16[DI] |

| DE06nn | FIADD i16[nn] | DE0Enn | FIMUL i16[nn] | DE16nn | FICOM i16[nn] | DE1Enn | FICOMP i16[nn] | DE26nn | FISUB i16[nn] | DE2Enn | FISUBR i16[nn] | DE36nn | FIDIV i16[nn] | DE3Enn | FIDIVR i16[nn] |

| DE07 | FIADD i16[BX] | DE0F | FIMUL i16[BX] | DE17 | FICOM i16[BX] | DE1F | FICOMP i16[BX] | DE27 | FISUB i16[BX] | DE2F | FISUBR i16[BX] | DE37 | FIDIV i16[BX] | DE3F | FIDIVR i16[BX] |

| DE40n | FIADD i16[BX+SI+n] | DE48n | FIMUL i16[BX+SI+n] | DE50n | FICOM i16[BX+SI+n] | DE58n | FICOMP i16[BX+SI+n] | DE60n | FISUB i16[BX+SI+n] | DE68n | FISUBR i16[BX+SI+n] | DE70n | FIDIV i16[BX+SI+n] | DE78n | FIDIVR i16[BX+SI+n] |

| DE41n | FIADD i16[BX+DI+n] | DE49n | FIMUL i16[BX+DI+n] | DE51n | FICOM i16[BX+DI+n] | DE59n | FICOMP i16[BX+DI+n] | DE61n | FISUB i16[BX+DI+n] | DE69n | FISUBR i16[BX+DI+n] | DE71n | FIDIV i16[BX+DI+n] | DE79n | FIDIVR i16[BX+DI+n] |

| DE42n | FIADD i16[BP+SI+n] | DE4An | FIMUL i16[BP+SI+n] | DE52n | FICOM i16[BP+SI+n] | DE5An | FICOMP i16[BP+SI+n] | DE62n | FISUB i16[BP+SI+n] | DE6An | FISUBR i16[BP+SI+n] | DE72n | FIDIV i16[BP+SI+n] | DE7An | FIDIVR i16[BP+SI+n] |

| DE43n | FIADD i16[BP+DI+n] | DE4Bn | FIMUL i16[BP+DI+n] | DE53n | FICOM i16[BP+DI+n] | DE5Bn | FICOMP i16[BP+DI+n] | DE63n | FISUB i16[BP+DI+n] | DE6Bn | FISUBR i16[BP+DI+n] | DE73n | FIDIV i16[BP+DI+n] | DE7Bn | FIDIVR i16[BP+DI+n] |

| DE44n | FIADD i16[SI+n] | DE4Cn | FIMUL i16[SI+n] | DE54n | FICOM i16[SI+n] | DE5Cn | FICOMP i16[SI+n] | DE64n | FISUB i16[SI+n] | DE6Cn | FISUBR i16[SI+n] | DE74n | FIDIV i16[SI+n] | DE7Cn | FIDIVR i16[SI+n] |

| DE45n | FIADD i16[DI+n] | DE4Dn | FIMUL i16[DI+n] | DE55n | FICOM i16[DI+n] | DE5Dn | FICOMP i16[DI+n] | DE65n | FISUB i16[DI+n] | DE6Dn | FISUBR i16[DI+n] | DE75n | FIDIV i16[DI+n] | DE7Dn | FIDIVR i16[DI+n] |

| DE46n | FIADD i16[BP+n] | DE4En | FIMUL i16[BP+n] | DE56n | FICOM i16[BP+n] | DE5En | FICOMP i16[BP+n] | DE66n | FISUB i16[BP+n] | DE6En | FISUBR i16[BP+n] | DE76n | FIDIV i16[BP+n] | DE7En | FIDIVR i16[BP+n] |

| DE47n | FIADD i16[BX+n] | DE4Fn | FIMUL i16[BX+n] | DE57n | FICOM i16[BX+n] | DE5Fn | FICOMP i16[BX+n] | DE67n | FISUB i16[BX+n] | DE6Fn | FISUBR i16[BX+n] | DE77n | FIDIV i16[BX+n] | DE7Fn | FIDIVR i16[BX+n] |

| DE80nn | FIADD i16[BX+SI+nn] | DE88nn | FIMUL i16[BX+SI+nn] | DE90nn | FICOM i16[BX+SI+nn] | DE98nn | FICOMP i16[BX+SI+nn] | DEA0nn | FISUB i16[BX+SI+nn] | DEA8nn | FISUBR i16[BX+SI+nn] | DEB0nn | FIDIV i16[BX+SI+nn] | DEB8nn | FIDIVR i16[BX+SI+nn] |

| DE81nn | FIADD i16[BX+DI+nn] | DE89nn | FIMUL i16[BX+DI+nn] | DE91nn | FICOM i16[BX+DI+nn] | DE99nn | FICOMP i16[BX+DI+nn] | DEA1nn | FISUB i16[BX+DI+nn] | DEA9nn | FISUBR i16[BX+DI+nn] | DEB1nn | FIDIV i16[BX+DI+nn] | DEB9nn | FIDIVR i16[BX+DI+nn] |

| DE82nn | FIADD i16[BP+SI+nn] | DE8Ann | FIMUL i16[BP+SI+nn] | DE92nn | FICOM i16[BP+SI+nn] | DE9Ann | FICOMP i16[BP+SI+nn] | DEA2nn | FISUB i16[BP+SI+nn] | DEAAnn | FISUBR i16[BP+SI+nn] | DEB2nn | FIDIV i16[BP+SI+nn] | DEBAnn | FIDIVR i16[BP+SI+nn] |

| DE83nn | FIADD i16[BP+DI+nn] | DE8Bnn | FIMUL i16[BP+DI+nn] | DE93nn | FICOM i16[BP+DI+nn] | DE9Bnn | FICOMP i16[BP+DI+nn] | DEA3nn | FISUB i16[BP+DI+nn] | DEABnn | FISUBR i16[BP+DI+nn] | DEB3nn | FIDIV i16[BP+DI+nn] | DEBBnn | FIDIVR i16[BP+DI+nn] |

| DE84nn | FIADD i16[SI+nn] | DE8Cnn | FIMUL i16[SI+nn] | DE94nn | FICOM i16[SI+nn] | DE9Cnn | FICOMP i16[SI+nn] | DEA4nn | FISUB i16[SI+nn] | DEACnn | FISUBR i16[SI+nn] | DEB4nn | FIDIV i16[SI+nn] | DEBCnn | FIDIVR i16[SI+nn] |

| DE85nn | FIADD i16[DI+nn] | DE8Dnn | FIMUL i16[DI+nn] | DE95nn | FICOM i16[DI+nn] | DE9Dnn | FICOMP i16[DI+nn] | DEA5nn | FISUB i16[DI+nn] | DEADnn | FISUBR i16[DI+nn] | DEB5nn | FIDIV i16[DI+nn] | DEBDnn | FIDIVR i16[DI+nn] |

| DE86nn | FIADD i16[BP+nn] | DE8Enn | FIMUL i16[BP+nn] | DE96nn | FICOM i16[BP+nn] | DE9Enn | FICOMP i16[BP+nn] | DEA6nn | FISUB i16[BP+nn] | DEAEnn | FISUBR i16[BP+nn] | DEB6nn | FIDIV i16[BP+nn] | DEBEnn | FIDIVR i16[BP+nn] |

| DE87nn | FIADD i16[BX+nn] | DE8Fnn | FIMUL i16[BX+nn] | DE97nn | FICOM i16[BX+nn] | DE9Fnn | FICOMP i16[BX+nn] | DEA7nn | FISUB i16[BX+nn] | DEAFnn | FISUBR i16[BX+nn] | DEB7nn | FIDIV i16[BX+nn] | DEBFnn | FIDIVR i16[BX+nn] |

| DA00 | FIADD i32[BX+SI] | DA08 | FIMUL i32[BX+SI] | DA10 | FICOM i32[BX+SI] | DA18 | FICOMP i32[BX+SI] | DA20 | FISUB i32[BX+SI] | DA28 | FISUBR i32[BX+SI] | DA30 | FIDIV i32[BX+SI] | DA38 | FIDIVR i32[BX+SI] |

| DA01 | FIADD i32[BX+DI] | DA09 | FIMUL i32[BX+DI] | DA11 | FICOM i32[BX+DI] | DA19 | FICOMP i32[BX+DI] | DA21 | FISUB i32[BX+DI] | DA29 | FISUBR i32[BX+DI] | DA31 | FIDIV i32[BX+DI] | DA39 | FIDIVR i32[BX+DI] |

| DA02 | FIADD i32[BP+SI] | DA0A | FIMUL i32[BP+SI] | DA12 | FICOM i32[BP+SI] | DA1A | FICOMP i32[BP+SI] | DA22 | FISUB i32[BP+SI] | DA2A | FISUBR i32[BP+SI] | DA32 | FIDIV i32[BP+SI] | DA3A | FIDIVR i32[BP+SI] |

| DA03 | FIADD i32[BP+DI] | DA0B | FIMUL i32[BP+DI] | DA13 | FICOM i32[BP+DI] | DA1B | FICOMP i32[BP+DI] | DA23 | FISUB i32[BP+DI] | DA2B | FISUBR i32[BP+DI] | DA33 | FIDIV i32[BP+DI] | DA3B | FIDIVR i32[BP+DI] |

| DA04 | FIADD i32[SI] | DA0C | FIMUL i32[SI] | DA14 | FICOM i32[SI] | DA1C | FICOMP i32[SI] | DA24 | FISUB i32[SI] | DA2C | FISUBR i32[SI] | DA34 | FIDIV i32[SI] | DA3C | FIDIVR i32[SI] |

| DA05 | FIADD i32[DI] | DA0D | FIMUL i32[DI] | DA15 | FICOM i32[DI] | DA1D | FICOMP i32[DI] | DA25 | FISUB i32[DI] | DA2D | FISUBR i32[DI] | DA35 | FIDIV i32[DI] | DA3D | FIDIVR i32[DI] |

| DA06nn | FIADD i32[nn] | DA0Enn | FIMUL i32[nn] | DA16nn | FICOM i32[nn] | DA1Enn | FICOMP i32[nn] | DA26nn | FISUB i32[nn] | DA2Enn | FISUBR i32[nn] | DA36nn | FIDIV i32[nn] | DA3Enn | FIDIVR i32[nn] |

| DA07 | FIADD i32[BX] | DA0F | FIMUL i32[BX] | DA17 | FICOM i32[BX] | DA1F | FICOMP i32[BX] | DA27 | FISUB i32[BX] | DA2F | FISUBR i32[BX] | DA37 | FIDIV i32[BX] | DA3F | FIDIVR i32[BX] |

| DA40n | FIADD i32[BX+SI+n] | DA48n | FIMUL i32[BX+SI+n] | DA50n | FICOM i32[BX+SI+n] | DA58n | FICOMP i32[BX+SI+n] | DA60n | FISUB i32[BX+SI+n] | DA68n | FISUBR i32[BX+SI+n] | DA70n | FIDIV i32[BX+SI+n] | DA78n | FIDIVR i32[BX+SI+n] |

| DA41n | FIADD i32[BX+DI+n] | DA49n | FIMUL i32[BX+DI+n] | DA51n | FICOM i32[BX+DI+n] | DA59n | FICOMP i32[BX+DI+n] | DA61n | FISUB i32[BX+DI+n] | DA69n | FISUBR i32[BX+DI+n] | DA71n | FIDIV i32[BX+DI+n] | DA79n | FIDIVR i32[BX+DI+n] |

| DA42n | FIADD i32[BP+SI+n] | DA4An | FIMUL i32[BP+SI+n] | DA52n | FICOM i32[BP+SI+n] | DA5An | FICOMP i32[BP+SI+n] | DA62n | FISUB i32[BP+SI+n] | DA6An | FISUBR i32[BP+SI+n] | DA72n | FIDIV i32[BP+SI+n] | DA7An | FIDIVR i32[BP+SI+n] |

| DA43n | FIADD i32[BP+DI+n] | DA4Bn | FIMUL i32[BP+DI+n] | DA53n | FICOM i32[BP+DI+n] | DA5Bn | FICOMP i32[BP+DI+n] | DA63n | FISUB i32[BP+DI+n] | DA6Bn | FISUBR i32[BP+DI+n] | DA73n | FIDIV i32[BP+DI+n] | DA7Bn | FIDIVR i32[BP+DI+n] |

| DA44n | FIADD i32[SI+n] | DA4Cn | FIMUL i32[SI+n] | DA54n | FICOM i32[SI+n] | DA5Cn | FICOMP i32[SI+n] | DA64n | FISUB i32[SI+n] | DA6Cn | FISUBR i32[SI+n] | DA74n | FIDIV i32[SI+n] | DA7Cn | FIDIVR i32[SI+n] |

| DA45n | FIADD i32[DI+n] | DA4Dn | FIMUL i32[DI+n] | DA55n | FICOM i32[DI+n] | DA5Dn | FICOMP i32[DI+n] | DA65n | FISUB i32[DI+n] | DA6Dn | FISUBR i32[DI+n] | DA75n | FIDIV i32[DI+n] | DA7Dn | FIDIVR i32[DI+n] |

| DA46n | FIADD i32[BP+n] | DA4En | FIMUL i32[BP+n] | DA56n | FICOM i32[BP+n] | DA5En | FICOMP i32[BP+n] | DA66n | FISUB i32[BP+n] | DA6En | FISUBR i32[BP+n] | DA76n | FIDIV i32[BP+n] | DA7En | FIDIVR i32[BP+n] |

| DA47n | FIADD i32[BX+n] | DA4Fn | FIMUL i32[BX+n] | DA57n | FICOM i32[BX+n] | DA5Fn | FICOMP i32[BX+n] | DA67n | FISUB i32[BX+n] | DA6Fn | FISUBR i32[BX+n] | DA77n | FIDIV i32[BX+n] | DA7Fn | FIDIVR i32[BX+n] |

| DA80nn | FIADD i32[BX+SI+nn] | DA88nn | FIMUL i32[BX+SI+nn] | DA90nn | FICOM i32[BX+SI+nn] | DA98nn | FICOMP i32[BX+SI+nn] | DAA0nn | FISUB i32[BX+SI+nn] | DAA8nn | FISUBR i32[BX+SI+nn] | DAB0nn | FIDIV i32[BX+SI+nn] | DAB8nn | FIDIVR i32[BX+SI+nn] |

| DA81nn | FIADD i32[BX+DI+nn] | DA89nn | FIMUL i32[BX+DI+nn] | DA91nn | FICOM i32[BX+DI+nn] | DA99nn | FICOMP i32[BX+DI+nn] | DAA1nn | FISUB i32[BX+DI+nn] | DAA9nn | FISUBR i32[BX+DI+nn] | DAB1nn | FIDIV i32[BX+DI+nn] | DAB9nn | FIDIVR i32[BX+DI+nn] |

| DA82nn | FIADD i32[BP+SI+nn] | DA8Ann | FIMUL i32[BP+SI+nn] | DA92nn | FICOM i32[BP+SI+nn] | DA9Ann | FICOMP i32[BP+SI+nn] | DAA2nn | FISUB i32[BP+SI+nn] | DAAAnn | FISUBR i32[BP+SI+nn] | DAB2nn | FIDIV i32[BP+SI+nn] | DABAnn | FIDIVR i32[BP+SI+nn] |

| DA83nn | FIADD i32[BP+DI+nn] | DA8Bnn | FIMUL i32[BP+DI+nn] | DA93nn | FICOM i32[BP+DI+nn] | DA9Bnn | FICOMP i32[BP+DI+nn] | DAA3nn | FISUB i32[BP+DI+nn] | DAABnn | FISUBR i32[BP+DI+nn] | DAB3nn | FIDIV i32[BP+DI+nn] | DABBnn | FIDIVR i32[BP+DI+nn] |

| DA84nn | FIADD i32[SI+nn] | DA8Cnn | FIMUL i32[SI+nn] | DA94nn | FICOM i32[SI+nn] | DA9Cnn | FICOMP i32[SI+nn] | DAA4nn | FISUB i32[SI+nn] | DAACnn | FISUBR i32[SI+nn] | DAB4nn | FIDIV i32[SI+nn] | DABCnn | FIDIVR i32[SI+nn] |

| DA85nn | FIADD i32[DI+nn] | DA8Dnn | FIMUL i32[DI+nn] | DA95nn | FICOM i32[DI+nn] | DA9Dnn | FICOMP i32[DI+nn] | DAA5nn | FISUB i32[DI+nn] | DAADnn | FISUBR i32[DI+nn] | DAB5nn | FIDIV i32[DI+nn] | DABDnn | FIDIVR i32[DI+nn] |

| DA86nn | FIADD i32[BP+nn] | DA8Enn | FIMUL i32[BP+nn] | DA96nn | FICOM i32[BP+nn] | DA9Enn | FICOMP i32[BP+nn] | DAA6nn | FISUB i32[BP+nn] | DAAEnn | FISUBR i32[BP+nn] | DAB6nn | FIDIV i32[BP+nn] | DABEnn | FIDIVR i32[BP+nn] |

| DA87nn | FIADD i32[BX+nn] | DA8Fnn | FIMUL i32[BX+nn] | DA97nn | FICOM i32[BX+nn] | DA9Fnn | FICOMP i32[BX+nn] | DAA7nn | FISUB i32[BX+nn] | DAAFnn | FISUBR i32[BX+nn] | DAB7nn | FIDIV i32[BX+nn] | DABFnn | FIDIVR i32[BX+nn] |

| D8C0 | FADD ST,ST0 | D8C8 | FMUL ST,ST0 | D8D0 | FCOM ST0 | D8D8 | FCOMP ST0 | D8E0 | FSUB ST,ST0 | D8E8 | FSUBR ST,ST0 | D8F0 | FDIV ST,ST0 | D8F8 | FDIVR ST,ST0 |

| D8C1 | FADD ST,ST1 | D8C9 | FMUL ST,ST1 | D8D1 | FCOM ST1 | D8D9 | FCOMP ST1 | D8E1 | FSUB ST,ST1 | D8E9 | FSUBR ST,ST1 | D8F1 | FDIV ST,ST1 | D8F9 | FDIVR ST,ST1 |

| D8C2 | FADD ST,ST2 | D8CA | FMUL ST,ST2 | D8D2 | FCOM ST2 | D8DA | FCOMP ST2 | D8E2 | FSUB ST,ST2 | D8EA | FSUBR ST,ST2 | D8F2 | FDIV ST,ST2 | D8FA | FDIVR ST,ST2 |

| D8C3 | FADD ST,ST3 | D8CB | FMUL ST,ST3 | D8D3 | FCOM ST3 | D8DB | FCOMP ST3 | D8E3 | FSUB ST,ST3 | D8EB | FSUBR ST,ST3 | D8F3 | FDIV ST,ST3 | D8FB | FDIVR ST,ST3 |

| D8C4 | FADD ST,ST4 | D8CC | FMUL ST,ST4 | D8D4 | FCOM ST4 | D8DC | FCOMP ST4 | D8E4 | FSUB ST,ST4 | D8EC | FSUBR ST,ST4 | D8F4 | FDIV ST,ST4 | D8FC | FDIVR ST,ST4 |

| D8C5 | FADD ST,ST5 | D8CD | FMUL ST,ST5 | D8D5 | FCOM ST5 | D8DD | FCOMP ST5 | D8E5 | FSUB ST,ST5 | D8ED | FSUBR ST,ST5 | D8F5 | FDIV ST,ST5 | D8FD | FDIVR ST,ST5 |

| D8C6 | FADD ST,ST6 | D8CE | FMUL ST,ST6 | D8D6 | FCOM ST6 | D8DE | FCOMP ST6 | D8E6 | FSUB ST,ST6 | D8EE | FSUBR ST,ST6 | D8F6 | FDIV ST,ST6 | D8FE | FDIVR ST,ST6 |

| D8C7 | FADD ST,ST7 | D8CF | FMUL ST,ST7 | D8D7 | FCOM ST7 | D8DF | FCOMP ST7 | D8E7 | FSUB ST,ST7 | D8EF | FSUBR ST,ST7 | D8F7 | FDIV ST,ST7 | D8FF | FDIVR ST,ST7 |

| DCC0 | FADD ST0,ST | DCC8 | FMUL ST0,ST | DCE0 | FSUBR ST0,ST | DCE8 | FSUB ST0,ST | DCF0 | FDIVR ST0,ST | DCF8 | FDIV ST0,ST | ||||

| DCC1 | FADD ST1,ST | DCC9 | FMUL ST1,ST | DCE1 | FSUBR ST1,ST | DCE9 | FSUB ST1,ST | DCF1 | FDIVR ST1,ST | DCF9 | FDIV ST1,ST | ||||

| DCC2 | FADD ST2,ST | DCCA | FMUL ST2,ST | DCE2 | FSUBR ST2,ST | DCEA | FSUB ST2,ST | DCF2 | FDIVR ST2,ST | DCFA | FDIV ST2,ST | ||||

| DCC3 | FADD ST3,ST | DCCB | FMUL ST3,ST | DCE3 | FSUBR ST3,ST | DCEB | FSUB ST3,ST | DCF3 | FDIVR ST3,ST | DCFB | FDIV ST3,ST | ||||

| DCC4 | FADD ST4,ST | DCCC | FMUL ST4,ST | DCE4 | FSUBR ST4,ST | DCEC | FSUB ST4,ST | DCF4 | FDIVR ST4,ST | DCFC | FDIV ST4,ST | ||||

| DCC5 | FADD ST5,ST | DCCD | FMUL ST5,ST | DCE5 | FSUBR ST5,ST | DCED | FSUB ST5,ST | DCF5 | FDIVR ST5,ST | DCFD | FDIV ST5,ST | ||||

| DCC6 | FADD ST6,ST | DCCE | FMUL ST6,ST | DCE6 | FSUBR ST6,ST | DCEE | FSUB ST6,ST | DCF6 | FDIVR ST6,ST | DCFE | FDIV ST6,ST | ||||

| DCC7 | FADD ST7,ST | DCCF | FMUL ST7,ST | DCE7 | FSUBR ST7,ST | DCEF | FSUB ST7,ST | DCF7 | FDIVR ST7,ST | DCFF | FDIV ST7,ST | ||||

| DEC0 | FADDP ST0,ST | DEC8 | FMULP ST0,ST | DED0 | FCOMP ST0 | DEE0 | FSUBRP ST0,ST | DEE8 | FSUBP ST0,ST | DEF0 | FDIVRP ST0,ST | DEF8 | FDIVP ST0,ST | ||

| DEC1 | FADDP ST1,ST | DEC9 | FMULP ST1,ST | DED1 | FCOMP ST1 | DED9 | FCOMPP ST1 | DEE1 | FSUBRP ST1,ST | DEE9 | FSUBP ST1,ST | DEF1 | FDIVRP ST1,ST | DEF9 | FDIVP ST1,ST |

| DEC2 | FADDP ST2,ST | DECA | FMULP ST2,ST | DED2 | FCOMP ST2 | DEE2 | FSUBRP ST2,ST | DEEA | FSUBP ST2,ST | DEF2 | FDIVRP ST2,ST | DEFA | FDIVP ST2,ST | ||

| DEC3 | FADDP ST3,ST | DECB | FMULP ST3,ST | DED3 | FCOMP ST3 | DEE3 | FSUBRP ST3,ST | DEEB | FSUBP ST3,ST | DEF3 | FDIVRP ST3,ST | DEFB | FDIVP ST3,ST | ||

| DEC4 | FADDP ST4,ST | DECC | FMULP ST4,ST | DED4 | FCOMP ST4 | DEE4 | FSUBRP ST4,ST | DEEC | FSUBP ST4,ST | DEF4 | FDIVRP ST4,ST | DEFC | FDIVP ST4,ST | ||

| DEC5 | FADDP ST5,ST | DECD | FMULP ST5,ST | DED5 | FCOMP ST5 | DEE5 | FSUBRP ST5,ST | DEED | FSUBP ST5,ST | DEF5 | FDIVRP ST5,ST | DEFD | FDIVP ST5,ST | ||

| DEC6 | FADDP ST6,ST | DECE | FMULP ST6,ST | DED6 | FCOMP ST6 | DEE6 | FSUBRP ST6,ST | DEEE | FSUBP ST6,ST | DEF6 | FDIVRP ST6,ST | DEFE | FDIVP ST6,ST | ||

| DEC7 | FADDP ST7,ST | DECF | FMULP ST7,ST | DED7 | FCOMP ST7 | DEE7 | FSUBRP ST7,ST | DEEF | FSUBP ST7,ST | DEF7 | FDIVRP ST7,ST | DEFF | FDIVP ST7,ST | ||

| DAC0 | FCMOVB ST0 | DAC8 | FCMOVE ST0 | DAD0 | FCMOVB ST0 | DAD8 | FCMOVU ST0 | ||||||||

| DAC1 | FCMOVB ST1 | DAC9 | FCMOVE ST1 | DAD1 | FCMOVB ST1 | DAD9 | FCMOVU ST1 | DAE9 | FUCOMP | ||||||

| DAC2 | FCMOVB ST2 | DACA | FCMOVE ST2 | DAD2 | FCMOVB ST2 | DADA | FCMOVU ST2 | ||||||||

| DAC3 | FCMOVB ST3 | DACB | FCMOVE ST3 | DAD3 | FCMOVB ST3 | DADB | FCMOVU ST3 | ||||||||

| DAC4 | FCMOVB ST4 | DACC | FCMOVE ST4 | DAD4 | FCMOVB ST4 | DADC | FCMOVU ST4 | ||||||||

| DAC5 | FCMOVB ST5 | DACD | FCMOVE ST5 | DAD5 | FCMOVB ST5 | DADD | FCMOVU ST5 | ||||||||

| DAC6 | FCMOVB ST6 | DACE | FCMOVE ST6 | DAD6 | FCMOVB ST6 | DADE | FCMOVU ST6 | ||||||||

| DAC7 | FCMOVB ST7 | DACF | FCMOVE ST7 | DAD7 | FCMOVB ST7 | DADF | FCMOVU ST7 | ||||||||

| Opcode | Mnemo | Opcode | Mnemo | Opcode | Mnemo | Opcode | Mnemo | Opcode | Mnemo | Opcode | Mnemo | Opcode | Mnemo | Opcode | Mnemo |

| D900 | FLD f32[BX+SI] | D910 | FST f32[BX+SI] | D918 | FSTP f32[BX+SI] | D938 | FSTCW u16[BX+SI] | D920 | FLDENV env[BX+SI] | D930 | FSTENV env[BX+SI] | D928 | FLDCW u16[BX+SI] | ||

| D901 | FLD f32[BX+DI] | D911 | FST f32[BX+DI] | D919 | FSTP f32[BX+DI] | D939 | FSTCW u16[BX+DI] | D921 | FLDENV env[BX+DI] | D931 | FSTENV env[BX+DI] | D929 | FLDCW u16[BX+DI] | ||

| D902 | FLD f32[BP+SI] | D912 | FST f32[BP+SI] | D91A | FSTP f32[BP+SI] | D93A | FSTCW u16[BP+SI] | D922 | FLDENV env[BP+SI] | D932 | FSTENV env[BP+SI] | D92A | FLDCW u16[BP+SI] | ||

| D903 | FLD f32[BP+DI] | D913 | FST f32[BP+DI] | D91B | FSTP f32[BP+DI] | D93B | FSTCW u16[BP+DI] | D923 | FLDENV env[BP+DI] | D933 | FSTENV env[BP+DI] | D92B | FLDCW u16[BP+DI] | ||

| D904 | FLD f32[SI] | D914 | FST f32[SI] | D91C | FSTP f32[SI] | D93C | FSTCW u16[SI] | D924 | FLDENV env[SI] | D934 | FSTENV env[SI] | D92C | FLDCW u16[SI] | ||

| D905 | FLD f32[DI] | D915 | FST f32[DI] | D91D | FSTP f32[DI] | D93D | FSTCW u16[DI] | D925 | FLDENV env[DI] | D935 | FSTENV env[DI] | D92D | FLDCW u16[DI] | ||

| D906nn | FLD f32[nn] | D916nn | FST f32[nn] | D91Enn | FSTP f32[nn] | D93Enn | FSTCW u16[nn] | D926nn | FLDENV env[nn] | D936nn | FSTENV env[nn] | D92Enn | FLDCW u16[nn] | ||

| D907 | FLD f32[BX] | D917 | FST f32[BX] | D91F | FSTP f32[BX] | D93F | FSTCW u16[BX] | D927 | FLDENV env[BX] | D937 | FSTENV env[BX] | D92F | FLDCW u16[BX] | ||

| D940n | FLD f32[BX+SI+n] | D950n | FST f32[BX+SI+n] | D958n | FSTP f32[BX+SI+n] | D978n | FSTCW u16[BX+SI+n] | D960n | FLDENV env[BX+SI+n] | D970n | FSTENV env[BX+SI+n] | D968n | FLDCW u16[BX+SI+n] | ||

| D941n | FLD f32[BX+DI+n] | D951n | FST f32[BX+DI+n] | D959n | FSTP f32[BX+DI+n] | D979n | FSTCW u16[BX+DI+n] | D961n | FLDENV env[BX+DI+n] | D971n | FSTENV env[BX+DI+n] | D969n | FLDCW u16[BX+DI+n] | ||

| D942n | FLD f32[BP+SI+n] | D952n | FST f32[BP+SI+n] | D95An | FSTP f32[BP+SI+n] | D97An | FSTCW u16[BP+SI+n] | D962n | FLDENV env[BP+SI+n] | D972n | FSTENV env[BP+SI+n] | D96An | FLDCW u16[BP+SI+n] | ||

| D943n | FLD f32[BP+DI+n] | D953n | FST f32[BP+DI+n] | D95Bn | FSTP f32[BP+DI+n] | D97Bn | FSTCW u16[BP+DI+n] | D963n | FLDENV env[BP+DI+n] | D973n | FSTENV env[BP+DI+n] | D96Bn | FLDCW u16[BP+DI+n] | ||

| D944n | FLD f32[SI+n] | D954n | FST f32[SI+n] | D95Cn | FSTP f32[SI+n] | D97Cn | FSTCW u16[SI+n] | D964n | FLDENV env[SI+n] | D974n | FSTENV env[SI+n] | D96Cn | FLDCW u16[SI+n] | ||

| D945n | FLD f32[DI+n] | D955n | FST f32[DI+n] | D95Dn | FSTP f32[DI+n] | D97Dn | FSTCW u16[DI+n] | D965n | FLDENV env[DI+n] | D975n | FSTENV env[DI+n] | D96Dn | FLDCW u16[DI+n] | ||

| D946n | FLD f32[BP+n] | D956n | FST f32[BP+n] | D95En | FSTP f32[BP+n] | D97En | FSTCW u16[BP+n] | D966n | FLDENV env[BP+n] | D976n | FSTENV env[BP+n] | D96En | FLDCW u16[BP+n] | ||

| D947n | FLD f32[BX+n] | D957n | FST f32[BX+n] | D95Fn | FSTP f32[BX+n] | D97Fn | FSTCW u16[BX+n] | D967n | FLDENV env[BX+n] | D977n | FSTENV env[BX+n] | D96Fn | FLDCW u16[BX+n] | ||

| D980nn | FLD f32[BX+SI+nn] | D990nn | FST f32[BX+SI+nn] | D998nn | FSTP f32[BX+SI+nn] | D9B8nn | FSTCW u16[BX+SI+nn] | D9A0nn | FLDENV env[BX+SI+nn] | D9B0nn | FSTENV env[BX+SI+nn] | D9A8nn | FLDCW u16[BX+SI+nn] | ||

| D981nn | FLD f32[BX+DI+nn] | D991nn | FST f32[BX+DI+nn] | D999nn | FSTP f32[BX+DI+nn] | D9B9nn | FSTCW u16[BX+DI+nn] | D9A1nn | FLDENV envBX+DI+nn | D9B1nn | FSTENV envBX+DI+nn | D9A9nn | FLDCW u16[BX+DI+nn] | ||

| D982nn | FLD f32[BP+SI+nn] | D992nn | FST f32[BP+SI+nn] | D99Ann | FSTP f32[BP+SI+nn] | D9BAnn | FSTCW u16[BP+SI+nn] | D9A2nn | FLDENV envBP+SI+nn | D9B2nn | FSTENV envBP+SI+nn | D9AAnn | FLDCW u16[BP+SI+nn] | ||

| D983nn | FLD f32[BP+DI+nn] | D993nn | FST f32[BP+DI+nn] | D99Bnn | FSTP f32[BP+DI+nn] | D9BBnn | FSTCW u16[BP+DI+nn] | D9A3nn | FLDENV envBP+DI+nn | D9B3nn | FSTENV envBP+DI+nn | D9ABnn | FLDCW u16[BP+DI+nn] | ||

| D984nn | FLD f32[SI+nn] | D994nn | FST f32[SI+nn] | D99Cnn | FSTP f32[SI+nn] | D9BCnn | FSTCW u16[SI+nn] | D9A4nn | FLDENV envSI+nn | D9B4nn | FSTENV envSI+nn | D9ACnn | FLDCW u16[SI+nn] | ||

| D985nn | FLD f32[DI+nn] | D995nn | FST f32[DI+nn] | D99Dnn | FSTP f32[DI+nn] | D9BDnn | FSTCW u16[DI+nn] | D9A5nn | FLDENV envDI+nn | D9B5nn | FSTENV envDI+nn | D9ADnn | FLDCW u16[DI+nn] | ||

| D986nn | FLD f32[BP+nn] | D996nn | FST f32[BP+nn] | D99Enn | FSTP f32[BP+nn] | D9BEnn | FSTCW u16[BP+nn] | D9A6nn | FLDENV envBP+nn | D9B6nn | FSTENV envBP+nn | D9AEnn | FLDCW u16[BP+nn] | ||

| D987nn | FLD f32[BX+nn] | D997nn | FST f32[BX+nn] | D99Fnn | FSTP f32[BX+nn] | D9BFnn | FSTCW u16[BX+nn] | D9A7nn | FLDENV envBX+nn | D9B7nn | FSTENV envBX+nn | D9AFnn | FLDCW u16[BX+nn] | ||

| DD00 | FLD f64[BX+SI] | DD10 | FST f64[BX+SI] | DD18 | FSTP f64[BX+SI] | DD38 | FSTSW u16[BX+SI] | DD20 | FRSTOR stt[BX+SI] | DD30 | FSAVE stt[BX+SI] | ||||

| DD01 | FLD f64[BX+DI] | DD11 | FST f64[BX+DI] | DD19 | FSTP f64[BX+DI] | DD39 | FSTSW u16[BX+DI] | DD21 | FRSTOR stt[BX+DI] | DD31 | FSAVE stt[BX+DI] | ||||

| DD02 | FLD f64[BP+SI] | DD12 | FST f64[BP+SI] | DD1A | FSTP f64[BP+SI] | DD3A | FSTSW u16[BP+SI] | DD22 | FRSTOR stt[BP+SI] | DD32 | FSAVE stt[BP+SI] | ||||

| DD03 | FLD f64[BP+DI] | DD13 | FST f64[BP+DI] | DD1B | FSTP f64[BP+DI] | DD3B | FSTSW u16[BP+DI] | DD23 | FRSTOR stt[BP+DI] | DD33 | FSAVE stt[BP+DI] | ||||

| DD04 | FLD f64[SI] | DD14 | FST f64[SI] | DD1C | FSTP f64[SI] | DD3C | FSTSW u16[SI] | DD24 | FRSTOR stt[SI] | DD34 | FSAVE stt[SI] | ||||

| DD05 | FLD f64[DI] | DD15 | FST f64[DI] | DD1D | FSTP f64[DI] | DD3D | FSTSW u16[DI] | DD25 | FRSTOR stt[DI] | DD35 | FSAVE stt[DI] | ||||

| DD06nn | FLD f64[nn] | DD16nn | FST f64[nn] | DD1Enn | FSTP f64[nn] | DD3Enn | FSTSW u16[nn] | DD26nn | FRSTOR stt[nn] | DD36nn | FSAVE stt[nn] | ||||

| DD07 | FLD f64[BX] | DD17 | FST f64[BX] | DD1F | FSTP f64[BX] | DD3F | FSTSW u16[BX] | DD27 | FRSTOR stt[BX] | DD37 | FSAVE stt[BX] | ||||

| DD40n | FLD f64[BX+SI+n] | DD50n | FST f64[BX+SI+n] | DD58n | FSTP f64[BX+SI+n] | DD78n | FSTSW u16[BX+SI+n] | DD60n | FRSTOR stt[BX+SI+n] | DD70n | FSAVE stt[BX+SI+n] | ||||

| DD41n | FLD f64[BX+DI+n] | DD51n | FST f64[BX+DI+n] | DD59n | FSTP f64[BX+DI+n] | DD79n | FSTSW u16[BX+DI+n] | DD61n | FRSTOR stt[BX+DI+n] | DD71n | FSAVE stt[BX+DI+n] | ||||

| DD42n | FLD f64[BP+SI+n] | DD52n | FST f64[BP+SI+n] | DD5An | FSTP f64[BP+SI+n] | DD7An | FSTSW u16[BP+SI+n] | DD62n | FRSTOR stt[BP+SI+n] | DD72n | FSAVE stt[BP+SI+n] | ||||

| DD43n | FLD f64[BP+DI+n] | DD53n | FST f64[BP+DI+n] | DD5Bn | FSTP f64[BP+DI+n] | DD7Bn | FSTSW u16[BP+DI+n] | DD63n | FRSTOR stt[BP+DI+n] | DD73n | FSAVE stt[BP+DI+n] | ||||

| DD44n | FLD f64[SI+n] | DD54n | FST f64[SI+n] | DD5Cn | FSTP f64[SI+n] | DD7Cn | FSTSW u16[SI+n] | DD64n | FRSTOR stt[SI+n] | DD74n | FSAVE stt[SI+n] | ||||

| DD45n | FLD f64[DI+n] | DD55n | FST f64[DI+n] | DD5Dn | FSTP f64[DI+n] | DD7Dn | FSTSW u16[DI+n] | DD65n | FRSTOR stt[DI+n] | DD75n | FSAVE stt[DI+n] | ||||

| DD46n | FLD f64[BP+n] | DD56n | FST f64[BP+n] | DD5En | FSTP f64[BP+n] | DD7En | FSTSW u16[BP+n] | DD66n | FRSTOR stt[BP+n] | DD76n | FSAVE stt[BP+n] | ||||

| DD47n | FLD f64[BX+n] | DD57n | FST f64[BX+n] | DD5Fn | FSTP f64[BX+n] | DD7Fn | FSTSW u16[BX+n] | DD67n | FRSTOR stt[BX+n] | DD77n | FSAVE stt[BX+n] | ||||

| DD80nn | FLD f64[BX+SI+nn] | DD90nn | FST f64[BX+SI+nn] | DD98nn | FSTP f64[BX+SI+nn] | DDB8nn | FSTSW u16[BX+SI+nn] | DDA0nn | FRSTOR stt[BX+SI+nn] | DDB0nn | FSAVE stt[BX+SI+nn] | ||||

| DD81nn | FLD f64[BX+DI+nn] | DD91nn | FST f64[BX+DI+nn] | DD99nn | FSTP f64[BX+DI+nn] | DDB9nn | FSTSW u16[BX+DI+nn] | DDA1nn | FRSTOR stt[BX+DI+nn] | DDB1nn | FSAVE stt[BX+DI+nn] | ||||

| DD82nn | FLD f64[BP+SI+nn] | DD92nn | FST f64[BP+SI+nn] | DD9Ann | FSTP f64[BP+SI+nn] | DDBAnn | FSTSW u16[BP+SI+nn] | DDA2nn | FRSTOR stt[BP+SI+nn] | DDB2nn | FSAVE stt[BP+SI+nn] | ||||

| DD83nn | FLD f64[BP+DI+nn] | DD93nn | FST f64[BP+DI+nn] | DD9Bnn | FSTP f64[BP+DI+nn] | DDBBnn | FSTSW u16[BP+DI+nn] | DDA3nn | FRSTOR stt[BP+DI+nn] | DDB3nn | FSAVE stt[BP+DI+nn] | ||||

| DD84nn | FLD f64[SI+nn] | DD94nn | FST f64[SI+nn] | DD9Cnn | FSTP f64[SI+nn] | DDBCnn | FSTSW u16[SI+nn] | DDA4nn | FRSTOR stt[SI+nn] | DDB4nn | FSAVE stt[SI+nn] | ||||

| DD85nn | FLD f64[DI+nn] | DD95nn | FST f64[DI+nn] | DD9Dnn | FSTP f64[DI+nn] | DDBDnn | FSTSW u16[DI+nn] | DDA5nn | FRSTOR stt[DI+nn] | DDB5nn | FSAVE stt[DI+nn] | ||||

| DD86nn | FLD f64[BP+nn] | DD96nn | FST f64[BP+nn] | DD9Enn | FSTP f64[BP+nn] | DDBEnn | FSTSW u16[BP+nn] | DDA6nn | FRSTOR stt[BP+nn] | DDB6nn | FSAVE stt[BP+nn] | ||||

| DD87nn | FLD f64[BX+nn] | DD97nn | FST f64[BX+nn] | DD9Fnn | FSTP f64[BX+nn] | DDBFnn | FSTSW u16[BX+nn] | DDA7nn | FRSTOR stt[BX+nn] | DDB7nn | FSAVE stt[BX+nn] | ||||

| DF00 | FILD i16[BX+SI] | DF10 | FIST i16[BX+SI] | DF18 | FISTP i16[BX+SI] | DF38 | FISTP i64[BX+SI] | DF20 | FBLD bcd[BX+SI] | DF30 | FBSTP bcd[BX+SI] | DF28 | FILD i64[BX+SI] | ||

| DF01 | FILD i16[BX+DI] | DF11 | FIST i16[BX+DI] | DF19 | FISTP i16[BX+DI] | DF39 | FISTP i64[BX+DI] | DF21 | FBLD bcd[BX+DI] | DF31 | FBSTP bcd[BX+DI] | DF29 | FILD i64[BX+DI] | ||

| DF02 | FILD i16[BP+SI] | DF12 | FIST i16[BP+SI] | DF1A | FISTP i16[BP+SI] | DF3A | FISTP i64[BP+SI] | DF22 | FBLD bcd[BP+SI] | DF32 | FBSTP bcd[BP+SI] | DF2A | FILD i64[BP+SI] | ||

| DF03 | FILD i16[BP+DI] | DF13 | FIST i16[BP+DI] | DF1B | FISTP i16[BP+DI] | DF3B | FISTP i64[BP+DI] | DF23 | FBLD bcd[BP+DI] | DF33 | FBSTP bcd[BP+DI] | DF2B | FILD i64[BP+DI] | ||

| DF04 | FILD i16[SI] | DF14 | FIST i16[SI] | DF1C | FISTP i16[SI] | DF3C | FISTP i64[SI] | DF24 | FBLD bcd[SI] | DF34 | FBSTP bcd[SI] | DF2C | FILD i64[SI] | ||

| DF05 | FILD i16[DI] | DF15 | FIST i16[DI] | DF1D | FISTP i16[DI] | DF3D | FISTP i64[DI] | DF25 | FBLD bcd[DI] | DF35 | FBSTP bcd[DI] | DF2D | FILD i64[DI] | ||

| DF06nn | FILD i16[nn] | DF16nn | FIST i16[nn] | DF1Enn | FISTP i16[nn] | DF3Enn | FISTP i64[nn] | DF26nn | FBLD bcd[nn] | DF36nn | FBSTP bcd[nn] | DF2Enn | FILD i64[nn] | ||

| DF07 | FILD i16[BX] | DF17 | FIST i16[BX] | DF1F | FISTP i16[BX] | DF3F | FISTP i64[BX] | DF27 | FBLD bcd[BX] | DF37 | FBSTP bcd[BX] | DF2F | FILD i64[BX] | ||

| DF40n | FILD i16[BX+SI+n] | DF50n | FIST i16[BX+SI+n] | DF58n | FISTP i16[BX+SI+n] | DF78n | FISTP i64[BX+SI+n] | DF60n | FBLD bcd[BX+SI+n] | DF70n | FBSTP bcd[BX+SI+n] | DF68n | FILD i64[BX+SI+n] | ||

| DF41n | FILD i16[BX+DI+n] | DF51n | FIST i16[BX+DI+n] | DF59n | FISTP i16[BX+DI+n] | DF79n | FISTP i64[BX+DI+n] | DF61n | FBLD bcd[BX+DI+n] | DF71n | FBSTP bcd[BX+DI+n] | DF69n | FILD i64[BX+DI+n] | ||

| DF42n | FILD i16[BP+SI+n] | DF52n | FIST i16[BP+SI+n] | DF5An | FISTP i16[BP+SI+n] | DF7An | FISTP i64[BP+SI+n] | DF62n | FBLD bcd[BP+SI+n] | DF72n | FBSTP bcd[BP+SI+n] | DF6An | FILD i64[BP+SI+n] | ||

| DF43n | FILD i16[BP+DI+n] | DF53n | FIST i16[BP+DI+n] | DF5Bn | FISTP i16[BP+DI+n] | DF7Bn | FISTP i64[BP+DI+n] | DF63n | FBLD bcd[BP+DI+n] | DF73n | FBSTP bcd[BP+DI+n] | DF6Bn | FILD i64[BP+DI+n] | ||

| DF44n | FILD i16[SI+n] | DF54n | FIST i16[SI+n] | DF5Cn | FISTP i16[SI+n] | DF7Cn | FISTP i64[SI+n] | DF64n | FBLD bcd[SI+n] | DF74n | FBSTP bcd[SI+n] | DF6Cn | FILD i64[SI+n] | ||

| DF45n | FILD i16[DI+n] | DF55n | FIST i16[DI+n] | DF5Dn | FISTP i16[DI+n] | DF7Dn | FISTP i64[DI+n] | DF65n | FBLD bcd[DI+n] | DF75n | FBSTP bcd[DI+n] | DF6Dn | FILD i64[DI+n] | ||

| DF46n | FILD i16[BP+n] | DF56n | FIST i16[BP+n] | DF5En | FISTP i16[BP+n] | DF7En | FISTP i64[BP+n] | DF66n | FBLD bcd[BP+n] | DF76n | FBSTP bcd[BP+n] | DF6En | FILD i64[BP+n] | ||

| DF47n | FILD i16[BX+n] | DF57n | FIST i16[BX+n] | DF5Fn | FISTP i16[BX+n] | DF7Fn | FISTP i64[BX+n] | DF67n | FBLD bcd[BX+n] | DF77n | FBSTP bcd[BX+n] | DF6Fn | FILD i64[BX+n] | ||

| DF80nn | FILD i16[BX+SI+nn] | DF90nn | FIST i16[BX+SI+nn] | DF98nn | FISTP i16[BX+SI+nn] | DFB8nn | FISTP i64[BX+SI+nn] | DFA0nn | FBLD bcd[BX+SI+nn] | DFB0nn | FBSTP bcd[BX+SI+nn] | DFA8nn | FILD i64[BX+SI+nn] | ||

| DF81nn | FILD i16[BX+DI+nn] | DF91nn | FIST i16[BX+DI+nn] | DF99nn | FISTP i16[BX+DI+nn] | DFB9nn | FISTP i64[BX+DI+nn] | DFA1nn | FBLD bcd[BX+DI+nn] | DFB1nn | FBSTP bcd[BX+DI+nn] | DFA9nn | FILD i64[BX+DI+nn] | ||

| DF82nn | FILD i16[BP+SI+nn] | DF92nn | FIST i16[BP+SI+nn] | DF9Ann | FISTP i16[BP+SI+nn] | DFBAnn | FISTP i64[BP+SI+nn] | DFA2nn | FBLD bcd[BP+SI+nn] | DFB2nn | FBSTP bcd[BP+SI+nn] | DFAAnn | FILD i64[BP+SI+nn] | ||

| DF83nn | FILD i16[BP+DI+nn] | DF93nn | FIST i16[BP+DI+nn] | DF9Bnn | FISTP i16[BP+DI+nn] | DFBBnn | FISTP i64[BP+DI+nn] | DFA3nn | FBLD bcd[BP+DI+nn] | DFB3nn | FBSTP bcd[BP+DI+nn] | DFABnn | FILD i64[BP+DI+nn] | ||

| DF84nn | FILD i16[SI+nn] | DF94nn | FIST i16[SI+nn] | DF9Cnn | FISTP i16[SI+nn] | DFBCnn | FISTP i64[SI+nn] | DFA4nn | FBLD bcd[SI+nn] | DFB4nn | FBSTP bcd[SI+nn] | DFACnn | FILD i64[SI+nn] | ||

| DF85nn | FILD i16[DI+nn] | DF95nn | FIST i16[DI+nn] | DF9Dnn | FISTP i16[DI+nn] | DFBDnn | FISTP i64[DI+nn] | DFA5nn | FBLD bcd[DI+nn] | DFB5nn | FBSTP bcd[DI+nn] | DFADnn | FILD i64[DI+nn] | ||

| DF86nn | FILD i16[BP+nn] | DF96nn | FIST i16[BP+nn] | DF9Enn | FISTP i16[BP+nn] | DFBEnn | FISTP i64[BP+nn] | DFA6nn | FBLD bcd[BP+nn] | DFB6nn | FBSTP bcd[BP+nn] | DFAEnn | FILD i64[BP+nn] | ||

| DF87nn | FILD i16[BX+nn] | DF97nn | FIST i16[BX+nn] | DF9Fnn | FISTP i16[BX+nn] | DFBFnn | FISTP i64[BX+nn] | DFA7nn | FBLD bcd[BX+nn] | DFB7nn | FBSTP bcd[BX+nn] | DFAFnn | FILD i64[BX+nn] | ||

| DB00 | FILD i32[BX+SI] | DB10 | FIST i32[BX+SI] | DB18 | FISTP i32[BX+SI] | DB38 | FSTP f80[BX+SI] | DB28 | FLD f80[BX+SI] | ||||||

| DB01 | FILD i32[BX+DI] | DB11 | FIST i32[BX+DI] | DB19 | FISTP i32[BX+DI] | DB39 | FSTP f80[BX+DI] | DB29 | FLD f80[BX+DI] | ||||||

| DB02 | FILD i32[BP+SI] | DB12 | FIST i32[BP+SI] | DB1A | FISTP i32[BP+SI] | DB3A | FSTP f80[BP+SI] | DB2A | FLD f80[BP+SI] | ||||||

| DB03 | FILD i32[BP+DI] | DB13 | FIST i32[BP+DI] | DB1B | FISTP i32[BP+DI] | DB3B | FSTP f80[BP+DI] | DB2B | FLD f80[BP+DI] | ||||||

| DB04 | FILD i32[SI] | DB14 | FIST i32[SI] | DB1C | FISTP i32[SI] | DB3C | FSTP f80[SI] | DB2C | FLD f80[SI] | ||||||

| DB05 | FILD i32[DI] | DB15 | FIST i32[DI] | DB1D | FISTP i32[DI] | DB3D | FSTP f80[DI] | DB2D | FLD f80[DI] | ||||||

| DB06nn | FILD i32[nn] | DB16nn | FIST i32[nn] | DB1Enn | FISTP i32[nn] | DB3Enn | FSTP f80[nn] | DB2Enn | FLD f80[nn] | ||||||

| DB07 | FILD i32[BX] | DB17 | FIST i32[BX] | DB1F | FISTP i32[BX] | DB3F | FSTP f80[BX] | DB2F | FLD f80[BX] | ||||||

| DB40n | FILD i32[BX+SI+n] | DB50n | FIST i32[BX+SI+n] | DB58n | FISTP i32[BX+SI+n] | DB78n | FSTP f80[BX+SI+n] | DB68n | FLD f80[BX+SI+n] | ||||||

| DB41n | FILD i32[BX+DI+n] | DB51n | FIST i32[BX+DI+n] | DB59n | FISTP i32[BX+DI+n] | DB79n | FSTP f80[BX+DI+n] | DB69n | FLD f80[BX+DI+n] | ||||||

| DB42n | FILD i32[BP+SI+n] | DB52n | FIST i32[BP+SI+n] | DB5An | FISTP i32[BP+SI+n] | DB7An | FSTP f80[BP+SI+n] | DB6An | FLD f80[BP+SI+n] | ||||||

| DB43n | FILD i32[BP+DI+n] | DB53n | FIST i32[BP+DI+n] | DB5Bn | FISTP i32[BP+DI+n] | DB7Bn | FSTP f80[BP+DI+n] | DB6Bn | FLD f80[BP+DI+n] | ||||||

| DB44n | FILD i32[SI+n] | DB54n | FIST i32[SI+n] | DB5Cn | FISTP i32[SI+n] | DB7Cn | FSTP f80[SI+n] | DB6Cn | FLD f80[SI+n] | ||||||

| DB45n | FILD i32[DI+n] | DB55n | FIST i32[DI+n] | DB5Dn | FISTP i32[DI+n] | DB7Dn | FSTP f80[DI+n] | DB6Dn | FLD f80[DI+n] | ||||||

| DB46n | FILD i32[BP+n] | DB56n | FIST i32[BP+n] | DB5En | FISTP i32[BP+n] | DB7En | FSTP f80[BP+n] | DB6En | FLD f80[BP+n] | ||||||

| DB47n | FILD i32[BX+n] | DB57n | FIST i32[BX+n] | DB5Fn | FISTP i32[BX+n] | DB7Fn | FSTP f80[BX+n] | DB6Fn | FLD f80[BX+n] | ||||||

| DB80nn | FILD i32[BX+SI+nn] | DB90nn | FIST i32[BX+SI+nn] | DB98nn | FISTP i32[BX+SI+nn] | DBB8nn | FSTP f80[BX+SI+nn] | DBA8nn | FLD f80[BX+SI+nn] | ||||||

| DB81nn | FILD i32[BX+DI+nn] | DB91nn | FIST i32[BX+DI+nn] | DB99nn | FISTP i32[BX+DI+nn] | DBB9nn | FSTP f80[BX+DI+nn] | DBA9nn | FLD f80[BX+DI+nn] | ||||||

| DB82nn | FILD i32[BP+SI+nn] | DB92nn | FIST i32[BP+SI+nn] | DB9Ann | FISTP i32[BP+SI+nn] | DBBAnn | FSTP f80[BP+SI+nn] | DBAAnn | FLD f80[BP+SI+nn] | ||||||

| DB83nn | FILD i32[BP+DI+nn] | DB93nn | FIST i32[BP+DI+nn] | DB9Bnn | FISTP i32[BP+DI+nn] | DBBBnn | FSTP f80[BP+DI+nn] | DBABnn | FLD f80[BP+DI+nn] | ||||||

| DB84nn | FILD i32[SI+nn] | DB94nn | FIST i32[SI+nn] | DB9Cnn | FISTP i32[SI+nn] | DBBCnn | FSTP f80[SI+nn] | DBACnn | FLD f80[SI+nn] | ||||||

| DB85nn | FILD i32[DI+nn] | DB95nn | FIST i32[DI+nn] | DB9Dnn | FISTP i32[DI+nn] | DBBDnn | FSTP f80[DI+nn] | DBADnn | FLD f80[DI+nn] | ||||||

| DB86nn | FILD i32[BP+nn] | DB96nn | FIST i32[BP+nn] | DB9Enn | FISTP i32[BP+nn] | DBBEnn | FSTP f80[BP+nn] | DBAEnn | FLD f80[BP+nn] | ||||||

| DB87nn | FILD i32[BX+nn] | DB97nn | FIST i32[BX+nn] | DB9Fnn | FISTP i32[BX+nn] | DBBFnn | FSTP f80[BX+nn] | DBAFnn | FLD f80[BX+nn] | ||||||

| D9C0 | FLD ST0 | D9F8 | FPREM | D9E0 | FCHS | D9F0 | F2XM1 | D9E8 | FLD1 | D9C8 | FXCH ST0 | ||||

| D9C1 | FLD ST1 | D9F9 | FYL2XP | D9E1 | FABS | D9F1 | FYL2X | D9E9 | FLDL2T | D9C9 | FXCH ST1 | ||||

| D9C2 | FLD ST2 | D9FA | FSQRT | D9F2 | FPTAN | D9EA | FLDL2E | D9CA | FXCH ST2 | ||||||

| D9C3 | FLD ST3 | D9FB | FSINCO | D9F3 | FPATAN | D9EB | FLDPI | D9CB | FXCH ST3 | ||||||

| D9C4 | FLD ST4 | D9FC | FRNDIN | D9E4 | FTST | D9F4 | FXTRAC | D9EC | FLDLG2 | D9CC | FXCH ST4 | ||||

| D9C5 | FLD ST5 | D9FD | FSCALE | D9E5 | FXAM | D9F5 | FPREM1 | D9ED | FLDLN2 | D9CD | FXCH ST5 | ||||

| D9C6 | FLD ST6 | D9FE | FSIN | D9F6 | FDECST | D9EE | FLDZ | D9CE | FXCH ST6 | ||||||

| D9C7 | FLD ST7 | D9FF | FCOS | D9F7 | FINCST | D9CF | FXCH ST7 | ||||||||

| DDC0 | FFREE ST0 | DDD0 | FST ST0 | DDD8 | FSTP ST0 | DDE0 | FCOM ST0 | DDE8 | FCOMP ST0 | ||||||

| DDC1 | FFREE ST1 | DDD1 | FST ST1 | DDD9 | FSTP ST1 | DDE1 | FCOM ST1 | DDE9 | FCOMP ST1 | ||||||

| DDC2 | FFREE ST2 | DDD2 | FST ST2 | DDDA | FSTP ST2 | DDE2 | FCOM ST2 | DDEA | FCOMP ST2 | ||||||

| DDC3 | FFREE ST3 | DDD3 | FST ST3 | DDDB | FSTP ST3 | DDE3 | FCOM ST3 | DDEB | FCOMP ST3 | ||||||

| DDC4 | FFREE ST4 | DDD4 | FST ST4 | DDDC | FSTP ST4 | DDE4 | FCOM ST4 | DDEC | FCOMP ST4 | ||||||

| DDC5 | FFREE ST5 | DDD5 | FST ST5 | DDDD | FSTP ST5 | DDE5 | FCOM ST5 | DDED | FCOMP ST5 | ||||||

| DDC6 | FFREE ST6 | DDD6 | FST ST6 | DDDE | FSTP ST6 | DDE6 | FCOM ST6 | DDEE | FCOMP ST6 | ||||||

| DDC7 | FFREE ST7 | DDD7 | FST ST7 | DDDF | FSTP ST7 | DDE7 | FCOM ST7 | DDEF | FCOMP ST7 | ||||||

| DFC0 | FFREEP ST0 | DFE0 | FSTSW AX | DFF0 | FCOMIP ST0 | ||||||||||

| DFC1 | FFREEP ST1 | DFF1 | FCOMIP ST1 | ||||||||||||

| DFC2 | FFREEP ST2 | DFF2 | FCOMIP ST2 | ||||||||||||

| DFC3 | FFREEP ST3 | DFF3 | FCOMIP ST3 | ||||||||||||

| DFC4 | FFREEP ST4 | DFF4 | FCOMIP ST4 | ||||||||||||

| DFC5 | FFREEP ST5 | DFF5 | FCOMIP ST5 | ||||||||||||

| DFC6 | FFREEP ST6 | DFF6 | FCOMIP ST6 | ||||||||||||

| DFC7 | FFREEP ST7 | DFF7 | FCOMIP ST7 | ||||||||||||

| DBC0 | FCMOVN ST0 | DBD0 | FCMOVN ST0 | DBD8 | FCMOVN ST0 | DBE0 | FENI | DBF0 | FCOMI ST0 | DBC8 | FCMOVN ST0 | ||||

| DBC1 | FCMOVN ST1 | DBD1 | FCMOVN ST1 | DBD9 | FCMOVN ST1 | DBE1 | FDISI | DBF1 | FCOMI ST1 | DBC9 | FCMOVN ST1 | ||||

| DBC2 | FCMOVN ST2 | DBD2 | FCMOVN ST2 | DBDA | FCMOVN ST2 | DBE2 | FCLEX | DBF2 | FCOMI ST2 | DBCA | FCMOVN ST2 | ||||

| DBC3 | FCMOVN ST3 | DBD3 | FCMOVN ST3 | DBDB | FCMOVN ST3 | DBE3 | FINIT | DBF3 | FCOMI ST3 | DBCB | FCMOVN ST3 | ||||

| DBC4 | FCMOVN ST4 | DBD4 | FCMOVN ST4 | DBDC | FCMOVN ST4 | DBE4 | FSETPM | DBF4 | FCOMI ST4 | DBCC | FCMOVN ST4 | ||||

| DBC5 | FCMOVN ST5 | DBD5 | FCMOVN ST5 | DBDD | FCMOVN ST5 | DBF5 | FCOMI ST5 | DBCD | FCMOVN ST5 | ||||||

| DBC6 | FCMOVN ST6 | DBD6 | FCMOVN ST6 | DBDE | FCMOVN ST6 | DBF6 | FCOMI ST6 | DBCE | FCMOVN ST6 | ||||||

| DBC7 | FCMOVN ST7 | DBD7 | FCMOVN ST7 | DBDF | FCMOVN ST7 | DBF7 | FCOMI ST7 | DBCF | FCMOVN ST7 | ||||||

| Opcode | Mnemo | Opcode | Mnemo | Opcode | Mnemo | Opcode | Mnemo | Opcode | Mnemo | Opcode | Mnemo | Opcode | Mnemo | Opcode | Mnemo |

منابع

[ویرایش]- ↑ Shvets, Gennadiy (8 October 2011). "IBM 8087 floating-point unit". CPU World. Retrieved 1 December 2011.

- ↑ Shvets, Gennadiy (8 October 2011). "AMD 8087 floating-point unit". CPU World. Retrieved 1 December 2011.

- ↑ Shvets, Gennadiy (8 October 2011). "Cyrix 8087 floating-point unit". CPU World. Retrieved 1 December 2011.

- ↑

{{cite conference}}: Empty citation (help) - ↑ ۵٫۰ ۵٫۱ "8087". Coprocessor Dot Info. 2007. Archived from the original on 30 September 2011. Retrieved 1 December 2011.

- ↑ ۶٫۰ ۶٫۱ ۶٫۲ "Intel FPU". cpu-collection.de. 2011. Retrieved 1 December 2011.

- ↑ ۷٫۰ ۷٫۱ Scott Mueller, Upgrading and repairing PCs, second edition, Que Books, 1992 شابک ۰−۸۸۰۲۲−۸۵۶−۳, pages 395-403

- ↑ اینتل اطلاعات کامپوننت کاتالوگ 1980، کاتالوگ اینتل. C-864/280 / 150K / CP، صفحات 8-21، 8-28

- ↑ Sanchez & Canton 2007, p. 96.

- ↑

- ↑

- ↑ برنامهنویسی زبان و سیستم مجمع برای IBM PC و سازگاری، Karen A. Lemone، صفحه 302

- ↑ ۱۳٫۰ ۱۳٫۱ ۱۳٫۲ Shvets, Gennadiy (8 October 2011). "Intel 8087 family". CPU World. Retrieved 1 December 2011.

- ↑ Sanchez & Canton 2007, p. 110.

- ↑ برنامهنویسی زبان و سیستم مجمع برای IBM PC و Compatibles, Karen A. Lemone, p300

- ↑ Scott Mueller, Upgrading and repairing PCs, second edition, Que Books, 1992 شابک ۰−۸۸۰۲۲−۸۵۶−۳, pages 395-403

کتابشناسی

[ویرایش]- Sanchez, Julio; Canton, Maria P. (2007). Software Solutions for Engineers and Scientists. CRC Press. ISBN 1-4200-4302-1.

French

French Deutsch

Deutsch