Phase-locked loop

Il phase-locked loop, comunemente noto con la sigla PLL, è un circuito ampiamente utilizzato nell'elettronica per le telecomunicazioni. Esso costituisce un sistema di controllo automatico che consente di generare un segnale periodico la cui fase è in relazione fissa con quella di un segnale di riferimento. Il PLL è inoltre un classico esempio di applicazione all'elettronica del controllo in retroazione. A causa dell'uso comune della sigla, in letteratura non esiste una traduzione italiana univoca del termine: è difatti possibile trovare le forme "anello ad aggancio di fase", "circuito ad aggancio di fase", "maglia ad aggancio di fase" oppure "anello agganciato in fase" che è forse quella che meglio esplica il suo significato.

Finalità

[modifica | modifica wikitesto]Tale tipo di circuito si usa per diversi scopi quali:

- sintetizzatore di frequenza, essendo in grado di sintonizzare un oscillatore controllato in tensione (Voltage Controlled Oscillator o VCO, dispositivo in grado di produrre oscillazioni ad alta frequenza ma dotato di bassa precisione) con un oscillatore al quarzo (caratterizzato al contrario da una bassa frequenza di risonanza, spesso insufficiente nel campo delle telecomunicazioni, ma anche da precisione molto elevata);

- generatore di clock, soprattutto nei sistemi a microprocessore;

- demodulatore FM;

- sistema di clock recovery, finalizzato cioè all'estrazione del clock da un segnale aperiodico modulato.

Schema di base

[modifica | modifica wikitesto]

Un PLL tipico è composto generalmente da quattro moduli (visibili in figura):

- comparatore di fase;

- filtro passa-basso;

- oscillatore controllato in tensione (VCO - Voltage Controlled Oscillator);

- divisore di frequenza.

Quest'ultimo modulo è presente solo quando si usa il PLL come moltiplicatore di frequenza, cioè quando si vuole ottenere un segnale a una frequenza multipla di quella di un segnale di riferimento. rappresenta la frequenza del segnale di ingresso, la frequenza del segnale di uscita e la tensione in ingresso al VCO, che nel caso di utilizzo del PLL come demodulatore è l'uscita che viene effettivamente considerata.

Analogia

[modifica | modifica wikitesto]È possibile paragonare il funzionamento del PLL all'accordatura di uno strumento musicale a corda usando un diapason, che produce una frequenza di riferimento. La tensione della corda viene regolata fino a che non si sentono più battimenti: ciò infatti significa che la corda e il diapason vibrano alla medesima frequenza.

Nel caso del PLL, ciò si ottiene aggiustando la tensione elettrica in ingresso al VCO, che controlla la frequenza generata in uscita, fino a quando quest'ultima coincide con la frequenza del segnale d'ingresso.

Storia

[modifica | modifica wikitesto]

Le prime ricerche nel campo dei PLL risalgono al 1932[1][2]. In quegli anni, un gruppo di ricercatori britannici cercava di sviluppare un'alternativa al ricevitore supereterodina di Edwin Howard Armstrong, con l'intento di ottenere un sistema che avesse bisogno di meno circuiti di sintonia. Nacque così il ricevitore omodina o a conversione diretta, molto più semplice del supereterodina, in quanto composto solo da un oscillatore, un miscelatore o mixer e un amplificatore.

Il segnale dell'oscillatore locale viene sintonizzato direttamente con la frequenza che si desidera ricevere e miscelato in un mixer a prodotto con il segnale d'ingresso. In questa maniera il segnale risultante include direttamente l'informazione modulata originale. Il problema principale di tali ricevitori è il controllo preciso della frequenza dell'oscillatore locale, necessario per sintonizzare adeguatamente il segnale modulato. Si pensò quindi di applicare all'oscillatore un segnale automatico di correzione, in maniera da mantenerlo alla fase e frequenza desiderata. Tale tecnica, già conosciuta per i servocontrolli, fu descritta in un articolo del 1932 dallo scienziato francese Henri de Bellescize, nel giornale L'Onde Électrique[3].

Inizialmente il sistema omodina non ebbe molta fortuna, poiché il costo necessario per la creazione di un PLL con questa tecnica non giustificava i vantaggi che essa portava. Per il buon funzionamento del ricevitore è necessaria infatti una grandissima linearità e una certa insensibilità agli offset di corrente continua, due caratteristiche che in quel periodo non erano ancora ottenibili.

Una prima diffusione su vasta scala dei PLL la si ebbe nei ricevitori analogici per la televisione, dove un circuito con funzionalità simili fu usato per oltre tre decenni[2]. Nei sistemi che utilizzano il segnale televisivo standard il controllo degli sweep (deflessioni) orizzontali e verticali è realizzato tramite due generatori a dente di sega. Assieme a tali segnali sono trasmessi anche degli impulsi di temporizzazione che ne permettono la sincronizzazione, che inizialmente veniva effettuata mediante una tecnica di injection locking, funzionante però solo in assenza di forte rumore. Dalla fine degli anni trenta, utilizzando l'equivalente di un PLL, gli impulsi di temporizzazione vengono agganciati in maniera molto più efficiente anche in presenza di rumore di fondo[4].

Un'ulteriore importante applicazione dei PLL si sviluppò con l'introduzione della televisione a colori negli Stati Uniti tra la fine degli anni quaranta e l'inizio degli anni cinquanta[2]. La Federal Communications Commission decretò infatti che il nuovo segnale televisivo dovesse mantenere la compatibilità con i vecchi sistemi in bianco e nero, non allocando quindi una nuova banda per permettere la trasmissione dell'informazione cromatica a parte. Fu quindi necessario trasmettere tale informazione all'interno della banda del segnale già esistente, tramite una sottoportante a circa 3,58 MHz. L'informazione cromatica è però di tipo vettoriale, in quanto l'ampiezza del segnale rappresenta la saturazione mentre la tonalità viene ricavata dalla differenza di fase del segnale rispetto alla sottoportante a 3,58 MHz. Ciò rende necessaria la presenza di un circuito che consenta una perfetta sincronizzazione con la fase di un segnale di riferimento, applicazione tipica per un PLL.

Un'applicazione dei PLL simile alla precedente è necessaria anche per la trasmissione radiofonica in stereofonia a modulazione di frequenza[2]. Anche in questo caso ci fu l'esigenza di garantire la compatibilità con il sistema precedente, cioè quello monofonico. L'informazione stereofonica, cioè la differenza tra il canale sinistro e quello destro, viene quindi codificata con una sottoportante alla frequenza di 38 kHz, modulata con la tecnica DSB-SC. In questa maniera il ricevitore, generando una copia della sottoportante, può ottenere i canali destro e sinistro semplicemente sommando e sottraendo il segnale monofonico (che è la somma dei due canali) al segnale differenza. La ricostruzione del segnale differenza risulta molto semplificata se per la demodulazione viene usato un PLL.

La grande popolarità di questo circuito però nacque con lo sviluppo delle tecnologie integrate, che permettono di realizzare a bassi costi su un unico circuito integrato un intero PLL[5]. Dal 1969, quando la Signetics introdusse una linea di circuiti integrati monolitici che contenevano un PLL completo sul chip[6], gli impieghi applicativi si sono moltiplicati. Pochi anni più tardi la RCA introdusse il CD4046 CMOS Micropower Phase-Locked Loop, che divenne un popolarissimo circuito integrato[7]. Molte delle tecnologie all'avanguardia degli ultimi anni, tra le quali la telefonia cellulare, le comunicazioni wireless, il GPS e la televisione satellitare e sul digitale terrestre non sarebbero possibili senza l'utilizzo intensivo dei PLL.

Funzionamento di base

[modifica | modifica wikitesto]Si trascuri per il momento il divisore di frequenza, che come già accennato viene usato solo quando il PLL è usato per produrre un'oscillazione a frequenza multipla rispetto a quella di riferimento. Il segnale in ingresso e quello in uscita vengono confrontati tra loro dal comparatore di fase, che restituisce in uscita un segnale di "errore" relazionato con lo sfasamento dell'uscita rispetto all'ingresso. Se si desidera che le due oscillazioni siano accordate (cioè alla stessa frequenza), è sufficiente che tale errore sia costante nel tempo.

Questo segnale di "errore", opportunamente filtrato, raggiunge l'oscillatore controllato in tensione (VCO) che viene quindi forzato a produrre un'oscillazione a una frequenza maggiore o minore a seconda dell'entità del segnale in ingresso. L'uscita del VCO viene poi confrontata con il segnale di riferimento, essendo l'anello chiuso in retroazione negativa. A regime, il sistema tenderà a raggiungere uno stato in cui l'uscita del VCO e il segnale di riferimento hanno la stessa frequenza, ottenendo così la sintonizzazione del PLL. La velocità di risposta del circuito dipende dalle caratteristiche del filtro e del comparatore di fase e dalla sensibilità del VCO. Si noti che la presenza del filtro passa-basso è indispensabile per controllare la dinamica del sistema in retroazione e per eliminare componenti spurie in uscita dal comparatore di fase[N 1].

Riconsiderando ora il divisore, esso ricava un segnale sottomultiplo di quello generato dal VCO, ovvero con frequenza "scalata" di N, e lo riporta all'ingresso del comparatore di fase. A regime, la frequenza del segnale in uscita dal divisore () e di quello in ingresso () saranno uguali. Dato che , a regime si avrà:

quindi l'uscita del VCO oscilla a una frequenza multipla di quella dell'ingresso.

Esiste un'ulteriore versione del PLL, detta a pompa di carica, che sostituisce il comparatore di fase con un comparatore di fase e frequenza (phase-frequency detector, PFD), seguito in cascata da un circuito che ha il compito di trasformare l'errore di fase in un segnale di tensione in ingresso al VCO, chiamato charge pump (pompa di carica).

Applicazioni

[modifica | modifica wikitesto]I PLL sono usati principalmente per ottenere una sincronizzazione costante nel tempo e per assorbire le eventuali variazioni nella frequenza del segnale di riferimento. Nel campo delle telecomunicazioni vengono utilizzati sia nei ricevitori coerenti, dove cioè è necessario ricostruire la portante del segnale ricevuto, sia in quelli incoerenti. Nelle modulazioni coerenti infatti l'informazione è contenuta nella differenza di fase tra il segnale inviato e la portante, che quindi deve essere riestratta in fase di ricezione per ricavare il segnale utile. Del resto, anche in modulazioni tradizionalmente incoerenti, come la FM, l'ASK e la FSK può rendersi necessario, principalmente per motivi di reiezione del rumore, l'utilizzo di una versione coerente. Nei sistemi analogici, grazie all'uso delle PLL si riesce in effetti ad aumentare il rapporto segnale rumore e a ridurre il rumore introdotto dai battimenti, mentre in quelli numerici diventa possibile ridurre notevolmente gli effetti legati agli errori di campionamento quali l'ISI.

Anche nei trasmettitori radio i PLL sono molto usati specie come moltiplicatori di frequenza, cioè per sintetizzare le alte frequenze necessarie alla generazione del segnale da immettere nel canale (come somma di portante e segnale in banda base) a partire da un riferimento molto preciso ma a frequenza piuttosto bassa (generalmente fornito da un oscillatore al quarzo).

Demodulatore FM

[modifica | modifica wikitesto]

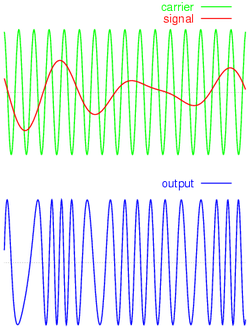

Se si vuole usare il PLL come demodulatore coerente, non è necessario utilizzare il divisore. Iniettando in ingresso un segnale modulato in frequenza, a regime anche l'uscita avrà la medesima modulazione poiché i due segnali sono agganciati in frequenza. Dato che l'ingresso del VCO è proprio il segnale che indica al componente come deve variare la frequenza, esso non è altro che il segnale modulante. È sufficiente quindi portare in uscita il segnale di ingresso del VCO a regime per avere l'informazione demodulata[8][9].

Sintetizzatore di frequenza

[modifica | modifica wikitesto]Se si vuole usare un PLL come sintetizzatore di frequenza, è invece necessaria la presenza di un divisore programmabile. Collegando in ingresso un oscillatore molto preciso, ad esempio al quarzo, in uscita si otterrà un segnale a frequenza N volte più alta rispetto all'ingresso ma con la medesima precisione (un oscillatore al quarzo può mantenere la deriva della propria frequenza di risonanza entro un intervallo di poche parti per milione[10]). Volendo variare la frequenza di oscillazione, è sufficiente variare tramite un segnale di controllo il modulo del divisore di frequenza.

Tale applicazione è molto utile in vari campi della trasmissione wireless[11], dal GSM[12] al CDMA[13], dove i PLL sono usati per la conversione in entrambi i sensi[14]. La sfida è riuscire a integrare sempre di più i componenti del PLL su un unico chip, in modo da ridurre il costo e la dimensione dei terminali cellulari. Tale tendenza si scontra con i requisiti imposti dagli standard, che rendono in alcuni casi necessaria la presenza di componenti discreti, e con l'impossibilità fisica di integrare alcune parti (tra tutte, il cristallo-quarzo).

Clock recovery

[modifica | modifica wikitesto]Nel caso si usi una modulazione coerente nel sistema di comunicazione, come detto è necessario ricostruire l'andamento temporale del clock per effettuare la demodulazione. Tale processo è detto estrazione del clock o clock recovery e può essere effettuato mediante un PLL[15]. Sempre in assenza del divisore, usando in ingresso il flusso di bit ricevuto, l'uscita del PLL a regime oscillerà in fase con il valore medio statistico del flusso di bit, che è tipicamente una sequenza di 1 e 0 alternati. L'uscita del PLL non è quindi altro che una replica del clock del segnale di partenza. Ciò permette di ricostruire la temporizzazione di un flusso di bit anche se esso non contiene informazioni sul clock.

Generazione e distribuzione del clock

[modifica | modifica wikitesto]

Per ottenere un clock preciso a frequenza di centinaia di megahertz o addirittura di alcuni gigahertz è necessario usare un PLL[16], che riesce ad agganciare il clock a un segnale di riferimento accurato ma a frequenze molto più basse, dell'ordine delle decine di megahertz. I moduli di moltiplicazione del divisore in questo caso possono essere anche molto elevati, vicini alle centinaia o alle migliaia.

Per ottenere una distribuzione del segnale più precisa, il clock di riferimento è quindi collegato a un PLL. L'uscita di questo pilota poi i circuiti driver che si occupano di distribuire il clock ai vari circuiti sequenziali. Una delle uscite del driver è riportata all'ingresso del PLL in modo da controllare la precisione del segnale di clock distribuito nel circuito. Dal punto di vista della teoria dei sistemi si può affermare che il PLL agisce come un filtro di Kalman.

Deskewing

[modifica | modifica wikitesto]Un clock trasmesso in parallelo con il flusso di dati permette di avere un riferimento per il campionamento. Poiché il segnale di temporizzazione viene amplificato prima di essere dato in ingresso ai flip-flop, sarà presente un ritardo (dipendente dalla temperatura, dalla tensione) tra il fronte del clock e la finestra temporale in cui è possibile ricevere i dati. Questo ritardo limita il massimo bitrate ottenibile nel protocollo. Per eliminare questo fenomeno, è possibile includere un PLL nel ricevitore, in modo da agganciare il flusso di dati al clock. I PLL usati in questo caso sono chiamati DLL, cioè delay-locked loop[17].

Spettro disperso

[modifica | modifica wikitesto]Tutti i sistemi elettronici emettono segnali indesiderati su frequenze radio e quindi sono potenziali sorgenti di interferenza verso altri sistemi che usano frequenze analoghe. Esiste un intero campo di studio, la compatibilità elettromagnetica, e svariate agenzie (tra cui la statunitense FCC e l'italiano CEI) che si occupano di questo problema. Le interferenze si manifestano generalmente sotto forma di picchi molto pronunciati alla frequenza di lavoro del dispositivo e a poche armoniche successive. Il PLL può essere usata anche in questo campo, per ridurre le interferenze con ricevitori ad alto fattore di merito. Variando infatti la frequenza di lavoro di una piccola quantità (circa l'1%) lo spettro di frequenze in cui l'interferenza si sviluppa è molto più ampio, ma i picchi divengono meno pronunciati. Un singolo ricevitore radio quindi, che tipicamente ha una banda molto limitata, capta solo una piccola parte della potenza totale degli interferenti e ciò riduce drasticamente il rumore. Tale tecnica è detta spettro disperso (spread spectrum)[18] ed è alla base del funzionamento dei dispositivi che operano nella banda libera intorno ai 2.4 GHz, come le comunicazioni wireless.

Ulteriori applicazioni

[modifica | modifica wikitesto]Tra le ulteriori applicazioni si citano:

- Demodulazione di segnali AM[19];

- Recupero di segnali di modesta entità che andrebbero persi a causa del rumore (lock-in amplifier)[20];

- Recupero della temporizzazione da flussi di dati provenienti da memorie di massa[21];

- Moltiplicatori di clock nei sistemi a microprocessore per ottenere frequenze di lavoro più elevate per alcuni componenti, mantenendo un preciso legame di temporizzazione con il clock principale[22];

- Decoder di tipo DTMF[23].

Analisi dei vari blocchi

[modifica | modifica wikitesto]Un PLL è un sistema composto per la gran parte da circuiti intrinsecamente non lineari, come il VCO, il comparatore di fase e il divisore di frequenza. Per poterne creare un modello matematico di facile manipolazione è quindi necessario linearizzare tali componenti in un punto di riposo e studiarne un modello alle variazioni[24]. Per fare ciò, risulta conveniente utilizzare come variabili di ingresso e uscita rispettivamente la fase del segnale di riferimento e quella del segnale di uscita del VCO . Si studierà quindi il comportamento dei vari blocchi considerando le variazioni di fase dei segnali rispetto a dei valori di riferimento.

Essendo inoltre il PLL un sistema in retroazione, le tecniche più adatte a descriverlo sono quelle dei controlli automatici, in quanto permettono di combinare il funzionamento dei vari componenti in un modello unico. Per fare ciò, è necessario applicare alle relazioni matematiche trovate la trasformata di Laplace.

Comparatore di fase

[modifica | modifica wikitesto]Il primo blocco del PLL è un comparatore di fase o phase detector (PD), cioè un circuito in grado di fornire un'uscita non nulla se i due segnali che ha in ingresso sono sfasati, ossia genera un'uscita che è una funzione dell'errore di fase. Il comparatore di fase può essere realizzato in vari modi, con implementazioni sia di tipo analogico che di tipo digitale[25].

Implementazione analogica

[modifica | modifica wikitesto]In versione analogica, un comparatore di fase non è altro che un miscelatore, ossia un circuito che produce in uscita un segnale pari al prodotto dei due ingressi. Si immagini di avere due ingressi del tipo e dove è un termine di differenza di fase tra i due segnali. L'uscita di un miscelatore con guadagno di conversione sarà quindi:

cioè la somma di due sinusoidi a pulsazioni pari alla somma e alla differenza delle pulsazioni dei segnali di ingresso. Per mantenere solo la sinusoide con la pulsazione differenza, il comparatore di fase è sempre seguito da un filtro passa-basso che elimina la sinusoide con pulsazione pari alla somma delle pulsazioni.

Si consideri ora il caso di . L'uscita del comparatore di fase diventa:

cioè la tensione d'uscita è uguale alla somma di una componente alternata, oscillante ad una frequenza doppia rispetto ai segnali di ingresso, e di una componente continua, la quale è funzione dello sfasamento tra i segnali

Tale relazione può essere linearizzata in un punto di riposo stabile, ad esempio . Così facendo si ottiene la caratteristica del comparatore di fase:

dove è lo scostamento della differenza di fase dal valore di riposo pari a . Tale segnale viene poi mandato al VCO che verrà quindi forzato ad aumentare o diminuire la frequenza di oscillazione.

Si può dimostrare che se l'uscita del comparatore di fase seguita dal filtro è in media nulla su intervallo di tempo dell'ordine dell'inverso della banda del filtro. Tale segnale contiene però delle componenti armoniche a una pulsazione . Se tale pulsazione è minore della banda del filtro, dopo un certo tempo il VCO riesce comunque ad agganciare il segnale di ingresso.

Sono possibili diverse implementazioni per questo mixer. Tra queste, le più frequenti sono la cosiddetta cella di Gilbert (detta anche moltiplicatore a quattro quadranti) oppure un mixer a ponte di diodi doppiamente bilanciato (vedi figura).

La presenza della componente a pulsazione (chiamata frequenza immagine) crea problemi in quanto non può mai essere completamente cancellata dal filtro. La presenza di questa componente spuria modula il VCO, che quindi non oscilla più a una frequenza molto precisa. Ciò causa un segnale di uscita spettralmente non puro, per via della presenza di due "code" spettrali ai lati della riga alla pulsazione voluta. Questo è un effetto indesiderato, perché non permette più di usare il PLL come riferimento preciso di oscillazione.

Implementazione digitale

[modifica | modifica wikitesto]

Tra i circuiti digitali più usati come comparatore di fase va citata la porta logica di tipo OR esclusivo (XOR)[26] che presenta una tabella di verità adatta per evidenziare le differenze:

| A | B | A⊕B |

|---|---|---|

| 1 | 1 | 0 |

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 0 | 0 | 0 |

Si vede infatti che quando i due segnali di ingresso hanno fasi opposte l'uscita è alta, mentre quando la fase è la stessa l'uscita è bassa. Complessivamente, considerando due segnali in ingresso con la stessa frequenza ma con fase diversa, l'uscita del comparatore sarà un treno di impulsi a frequenza doppia di quella delle onde in ingresso. Il duty cycle degli impulsi sarà proporzionale allo sfasamento tra le due onde. Si può quindi anche in questo caso scrivere:

dove è una costante ottenibile dalla linearizzazione della caratteristica del comparatore e è come in precedenza lo scostamento della differenza di fase dal valore di riposo, in questo caso pari a in un caso ideale. Questa approssimazione è possibile solo considerando la presenza del filtro passa-basso, al quale arriva in ingresso il treno di impulsi, che viene convertito in una tensione lentamente variabile a causa della banda passante stretta del filtro.

Si noti che per utilizzare la funzione OR esclusivo come comparatore di fase è necessario usare una porta logica di tipo differenziale, assegnando al valore logico 0 una tensione di uscita negativa. Se si assegnasse infatti al valore logico 0 una tensione nulla il VCO riceverebbe in ingresso una tensione o crescente o costante. Non sarebbe quindi possibile abbassarne la frequenza generata e il PLL non riuscirebbe ad agganciare segnali di ingresso in ritardo di fase con quelli di uscita ma solo quelli in anticipo.

Anche la funzione OR esclusivo, come il mixer analogico, fornisce in uscita un valore medio nullo se le due onde hanno frequenze diverse e anche in questo caso il VCO riesce ad agganciare l'ingresso solo se è minore della banda passante del filtro.

Un'implementazione digitale molto simile a quella con la funzione OR esclusivo si può ottenere con un flip-flop di tipo JK sensibile al fronte[27][28]. Un fronte sull'ingresso J porta l'uscita nello stato mentre un fronte sull'ingresso K lo porta nello stato . Il vantaggio è che il treno di impulsi ha una frequenza pari alla frequenza di ingresso e non pari al doppio come avviene nel caso della porta logica OR esclusivo.

Oscillatore controllato in tensione

[modifica | modifica wikitesto]

Il VCO all'interno del PLL è tipicamente un oscillatore di tipo LC. Questi oscillatori sono composti da un parallelo di un induttore e di un condensatore, che vanno in risonanza a una certa frequenza pari a:

Alla risonanza infatti il parallelo presenta un'impedenza infinita e c'è uno scambio di energia tra l'induttanza e la capacità, che teoricamente causa un'oscillazione periodica. A causa delle non-idealità dei componenti però, questa oscillazione verrebbe smorzata dalla presenza di perdite, rappresentabili circuitalmente come una resistenza in serie all'induttanza. Risulta quindi necessario creare un blocco circuitale che presenti una resistenza negativa, in modo da compensare le perdite. Questo viene fatto tipicamente mediante bipoli di tipo non lineare, ad esempio con la connessione incrociata di due transistor.

Un'importante caratteristica degli oscillatori è il loro fattore di merito (o di qualità) , cioè:

dove è la frequenza di risonanza, è la resistenza serie che schematizza le perdite del parallelo LC e è la banda passante del circuito. Si vorrebbe un fattore di qualità molto elevato, poiché significa avere meno rumore e banda passante più stretta, ma con implementazioni integrate raramente si ottengono valori di maggiori di 10.

Per variare la frequenza di oscillazione, l'unica maniera è variare il valore della capacità, poiché quello dell'induttanza è praticamente impossibile da modificare. Al posto delle capacità fisse si utilizzano quindi dei varactor, cioè dei diodi polarizzati in inversa, che sono caratterizzati da una capacità non lineare funzione della tensione inversa applicata. Variando quindi una tensione di controllo a uno dei capi del diodo è possibile ottenere un oscillatore con frequenza variabile.

Il VCO ha quindi una pulsazione di oscillazione di riposo (chiamata pulsazione di free-running ) che viene variata a seconda della tensione che viene data in ingresso al circuito. Considerando il segnale in uscita, esso sarà quindi del tipo[29]:

dove è una costante ottenuta dalla linearizzazione della caratteristica del varactor. Si può quindi affermare che, se si prende come ingresso la tensione e come uscita la fase, il VCO si comporta come un integratore. Sollecitandolo quindi con una rampa, esso produrrà un'oscillazione a frequenza fissa determinata dalla velocità della rampa medesima.

Riferimento di frequenza

[modifica | modifica wikitesto]

Utilizzando il PLL come sintetizzatore di frequenza è necessario porre in ingresso un segnale di riferimento con una frequenza molto ben controllata e stabile. Tipicamente si sceglie di usare un oscillatore al quarzo[30]. Il quarzo è infatti un materiale piezoelettrico, cioè in grado di trasformare oscillazioni meccaniche in oscillazioni elettriche e viceversa. Dal punto di vista elettrico, un quarzo è equivalente alla rete elettrica visibile in figura, che ha un comportamento induttivo per un range di frequenze molto stretto. Sostituendo l'induttanza di un oscillatore di Colpitts con il quarzo, si ottiene così un oscillatore con una frequenza molto bene determinata, perché compresa nella fascia di frequenze in cui il quarzo ha un comportamento induttivo. Il quarzo è inoltre caratterizzato da valori del fattore di qualità molto elevati, quindi il segnale di uscita del oscillatore sarà poco rumoroso. Il problema di tali oscillatori è che il quarzo è un componente discreto, che non può essere integrato, e ciò aumenta il costo e la complessità del progetto, benché il quarzo di per sé abbia un costo abbastanza contenuto.

Un altro tipo di oscillatori al quarzo sono i Surface acoustic wave (SAW), che sono più costosi ma anche più accurati degli oscillatori di tipo tradizionale[31]. Essi si basano sulla trasduzione di onde acustiche, di tipo meccanico, in onde di tipo elettrico mediante l'impiego di un piezoelettrico.

Se il PLL è usato all'interno di un microprocessore, è possibile usare come riferimento di frequenza un cosiddetto oscillatore ad anello, cioè una maglia con un numero dispari di invertitori logici[32]. Tale circuito non ha un singolo stato stabile per le tensioni interne alla maglia, perciò una transizione continua a propagarsi indefinitamente all'interno dell'anello. La frequenza può essere controllata variando la tensione di alimentazione oppure il carico capacitivo di ogni stadio.

Divisore di frequenza

[modifica | modifica wikitesto]

Come detto in precedenza, se si vuole usare un PLL per produrre un segnale oscillante preciso ad alta frequenza a partire da uno a frequenza più bassa è necessario inserire tra l'uscita e l'ingresso un divisore di frequenza per , che non è altro che una macchina a stati finiti che genera un solo fronte in uscita per ogni fronti in ingresso. In questo modo, si ottiene a regime un segnale in uscita con una frequenza pari a volte quella di ingresso.

Divisore intero

[modifica | modifica wikitesto]In molte applicazioni si desidera ottenere un segnale oscillante preciso ma a frequenza variabile, ad esempio per effettuare la sintonia di un ricevitore radio. Non potendo modificare il segnale di riferimento di ingresso (esso infatti deve essere il più stabile possibile per avere una buona purezza spettrale) si usa un divisore programmabile, nel quale il valore può essere variato tramite un segnale di controllo fornito da un microcontrollore.

I sintetizzatori di frequenza di questo tipo, che sono detti a N intero poiché consentono solo la divisione per un numero intero, permettono una variazione di frequenza minima pari alla frequenza del segnale di riferimento.

Alcuni PLL includono un divisore anche tra il segnale di riferimento e l'ingresso di riferimento del comparatore di fase. Se tale divisore ha modulo , a regime varrà la relazione:

In questa maniera, fissato il segnale di riferimento, è comunque possibile ottenere variazioni minime di frequenza più basse, pari a . Il problema di questo modo di procedere è che se si vuole variare di poco la frequenza di un segnale molto veloce (ad esempio variare di poche decine o centinaia di kilohertz un segnale a un gigahertz) il divisore che collega l'uscita all'ingresso deve avere . Ciò rende il divisore praticamente impossibile da realizzare e inoltre crea molti problemi di purezza spettrale, in quanto un valore elevato di aumenta il rumore sul segnale di uscita.

Divisore frazionario

[modifica | modifica wikitesto]Per risolvere tale problema, al posto dei divisori interi si usano i cosiddetti divisori frazionari[33]. Essi sono composti da un contatore per e da un divisore a modulo duale (dual modulus), ossia da un circuito capace di dividere, in base ad un segnale esterno di controllo, per due distinti valori (ad esempio /, ma sono comuni anche divisori per /). Il contatore conta i fronti in uscita al divisore e al -esimo fronte manda un segnale al divisore facendolo dividere per . Al -esimo fronte, il divisore torna a dividere per . Il segnale che arriva al comparatore di fase sarà quindi in media diviso per:

quindi è possibile mantenere fisso il valore , lasciandolo anche molto piccolo (ciò permette di usare segnali di riferimento a frequenza più alta), mentre il valore di può essere variato dal microcontrollore per ottenere la variazione di frequenza voluta.

Il contatore per è solitamente detto swallow counter.

Da notare che di solito i PLL combinano i meccanismi di divisione intera e frazionaria. Nei dispositivi commerciali è comune trovare un divisore intero (fatto da un contatore programmabile, per esempio 10 o 12 bit), più un divisore frazionario composto da swallow counter e contatore a modulo duale.

Il fatto che la divisione non venga eseguita in maniera precisa come nel caso del divisore intero ma solo come risultato di una media provoca la presenza di un rumore di quantizzazione aggiuntivo sul segnale all'uscita del divisore.

Modulatore delta-sigma

[modifica | modifica wikitesto]Il rumore di quantizzazione introdotto dal divisore frazionario può essere anche molto significativo perché spesso si concentra in una banda vicina a quella del segnale utile. Per risolvere questo problema si utilizzano i cosiddetti modulatori [34]. Diversamente dai divisori frazionari normali, in cui la sequenza di divisioni per o è periodica, nei modulatori delta-sigma la sequenza, pur ottenendo in media lo stesso risultato, è di tipo pseudo-casuale. Il vantaggio è che in questo caso il rumore di quantizzazione viene spostato verso le alte frequenze e può quindi essere agevolmente eliminato con un opportuno filtro.

Rappresentazione nel dominio di Laplace

[modifica | modifica wikitesto]Fissati i vari componenti appena descritti, resta da scegliere il filtro che deve controllare la dinamica della retroazione. Modellando un PLL come un sistema dinamico lineare stazionario, il suo comportamento si può descrivere come già detto tramite una funzione di trasferimento, ovvero usando il rapporto tra la trasformata di Laplace del segnale in uscita e la trasformata di Laplace del segnale di ingresso[35]. Si può quindi scrivere:

Per poter descrivere l'intero PLL è quindi necessario trasformare secondo Laplace tutte le relazioni ingresso-uscita dei singoli componenti. Si ottiene quindi per il comparatore di fase:

L'azione del comparatore di fase risulta quindi completamente di tipo proporzionale.

Prendendo come ingresso la tensione e in uscita la fase, il VCO come detto funziona come un integratore. Si ottiene quindi:

L'azione di controllo operata dal VCO è quindi di tipo PI, cioè proporzionale-integrativa.

Infine, il divisore ha una caratteristica del tipo . Essendo la frequenza la derivata della fase, la relazione può essere scritta equivalentemente come:

Applicando le regole per il calcolo della funzione di trasferimento di un sistema in retroazione, si ottiene (omettendo per semplicità la dipendenza dalla variabile ):

dove è la trasformata di Laplace della fase in uscita dal VCO, mentre è la trasformata di Laplace della fase del segnale in ingresso (tipicamente quello di riferimento). Ponendo si ottiene il caso di un PLL senza divisore di frequenza.

PLL del primo ordine

[modifica | modifica wikitesto]A seconda della funzione di trasferimento del filtro passa basso si ottengono PLL con comportamenti diversi. I PLL più semplici sono quelli in cui la funzione di trasferimento del filtro è una costante (cioè il filtro in realtà è un amplificatore o un attenuatore a banda larga). Applicando la formula precedentemente citata per la funzione di trasferimento complessiva della PLL si ottiene:

Tali PLL sono detti PLL del primo ordine[36] poiché la funzione di trasferimento complessiva del sistema è del prim'ordine (cioè ha un solo polo). Il guadagno e la banda passante risultano essere:

quindi c'è una relazione di proporzionalità inversa tra il guadagno e la banda del sistema.

Errore di fase a regime

[modifica | modifica wikitesto]

Si ponga in ingresso al PLL una rampa di fase, cioè una variazione istantanea di frequenza (funzione gradino) che può essere rappresentata con una funzione di trasferimento:

Si vuole calcolare la differenza di fase tra l'ingresso e l'uscita quando il PLL è a regime. Nel dominio di Laplace essa vale:

Applicando il teorema del valore finale, si ottiene:

cioè il PLL mantiene un errore a regime non nullo, tanto più piccolo quanto più grande è il guadagno . Per ottenere un errore di fase nullo sarebbe quindi necessario un guadagno infinito, ovviamente impossibile da realizzare. Inoltre, non può essere aumentato a piacere, poiché è inversamente proporzionale alla banda. Se si vuole ridurre il rumore presente sul segnale d'ingresso alle alte frequenze è infatti necessario avere un sistema a banda abbastanza stretta, e quindi un guadagno limitato.

PLL del secondo ordine

[modifica | modifica wikitesto]

I PLL del secondo ordine sono caratterizzati da una funzione di trasferimento complessiva a due poli (in base alla definizione di sistema del secondo ordine). Per ottenere tale funzione di trasferimento è necessario utilizzare un filtro passa-basso del primo ordine come il seguente:

dove è la frequenza di taglio del filtro. Tale filtro può essere ottenuto ad esempio con una semplice rete di tipo RC, con funzione di trasferimento:

dove la frequenza di taglio è pari a .

In tale maniera si ottiene per il PLL una funzione di trasferimento complessiva pari a[37]:

dove:

è il prodotto dei guadagni dei vari blocchi.

Si trascuri il prefattore che è una sorta di "guadagno di fase" del PLL. Confrontando il risultato ottenuto con la forma classica di un sistema del secondo ordine (oscillatore smorzato), ossia:

dove:

- è la pulsazione naturale, corrispondente all'incirca alla banda passante;

- è lo smorzamento;

si ricava:

Se si vuole un sistema che abbia una risposta veloce ma senza sovraelongazioni, è necessario scegliere , pari allo smorzamento critico. Ciò conduce a:

cioè una relazione ben precisa tra il prodotto dei guadagni e la banda del filtro passa basso.

Errore di fase a regime e tempo di assestamento

[modifica | modifica wikitesto]È possibile ripetere anche in questo caso il procedimento eseguito per un PLL del primo ordine. Si ottiene[38]:

cioè anche in questo caso il PLL mantiene un errore a regime non nullo, tanto più piccolo quanto più elevato è il guadagno . Come per i PLL del primo ordine, risulta utile aumentare , tenendo conto della sua proporzionalità con la banda del filtro , che va mantenuta non troppo elevata in modo da filtrare in maniera efficiente l'uscita del comparatore di fase.

Per quanto riguarda invece il tempo di assestamento del PLL, cioè il tempo necessario al sistema per andare a regime, sarà circa:

che significa che più è stretta la banda del filtro più aumenta il tempo di assestamento. Per questo tipo di PLL è quindi necessario operare un'ulteriore scelta di compromesso tra tempi di risposta veloci (che richiedono bande larghe) e un buon filtraggio del segnale del comparatore di fase (che richiede bande strette).

Filtro con zero

[modifica | modifica wikitesto]

È possibile modificare il filtro passa basso per ottenere diverse funzioni di trasferimento sempre del secondo ordine. Con due resistenze e un condensatore si può creare una rete con la relazione ingresso-uscita:

Questo filtro ha due costanti di tempo:

Sostituendo tale funzione di trasferimento in quella totale del PLL (trascurando il divisore di frequenza) si ottengono i seguenti valori per la frequenza naturale e per lo smorzamento:

Rispetto al PLL del secondo ordine è possibile scegliere indipendentemente i valori per e , dimensionando opportunamente le due resistenze e il condensatore. Si ricava infatti:

In base ai valori voluti di e e alle caratteristiche del comparatore di fase e del VCO è quindi possibile ricavare e , e da essi i valori dei passivi del filtro[39].

I filtri reali utilizzati nei PLL possono essere anche molto più complessi di questi, in modo da avere migliori prestazioni per quanto riguarda la riduzione del rumore di fase oppure di quello del segnale in ingresso[40].

PLL a pompa di carica

[modifica | modifica wikitesto]

Esiste un ulteriore tipo di PLL molto usato, detto PLL a pompa di carica[41]. Questo circuito al posto del comparatore di fase impiega un circuito digitale più complesso, chiamato comparatore di fase e frequenza (phase and frequency detector, PFD). Tale circuito, diversamente dai comparatori di fase classici, ha dei segnali d'uscita non nulli anche se le due frequenze in ingresso sono diverse. Il PFD ha due uscite, UP e DOWN, che possono avere alternativamente un segnale alto. Tali uscite sono collegate a un circuito chiamato pompa di carica (charge pump) che crea un segnale adatto a controllare il VCO. Il resto del circuito è simile a un PLL tradizionale.

I PLL a pompa di carica hanno svariati vantaggi rispetto ai PLL tradizionali. Come detto, l'uscita del PFD è non nulla anche in presenza di segnali a frequenze diverse. In questa maniera non è necessario mantenere la banda del filtro passa basso particolarmente alta per permettere al PLL di agganciare segnali con variazioni improvvise di frequenza. Avere una banda stretta è infatti importante perché permette di ridurre il rumore del segnale di riferimento in uscita. La pompa di carica inoltre ha la funzione di ulteriore integratore del segnale (oltre al VCO), permettendo quindi di avere un errore a regime nullo nel caso di una rampa di fase (gradino di frequenza).

Comparatore di fase e frequenza e pompa di carica

[modifica | modifica wikitesto]

Il comparatore di fase e frequenza è una macchina a stati finiti progettata per confrontare le frequenze e le fasi dei due segnali in ingresso. Una delle più semplici implementazioni del circuito è quella che utilizza due flip-flop di tipo D, come si può vedere nello schematico a destra. Nella figura sottostante si vede invece il diagramma degli stati, dove per e non si intendono i livelli ma i fronti positivi dei segnali ingresso, in quanto il PFD è appunto sensibile al fronte. Le uscite UP e DOWN del PFD pilotano un circuito chiamato pompa di carica, di cui esistono essenzialmente due versioni:

- pompa di carica di tipo bang-bang o push-pull. Tale circuito eroga in uscita una corrente I se UP è ad 1 e DOWN è a zero, una corrente -I nel caso opposto; in tutti gli altri casi il circuito è interdetto. Considerato il funzionamento logico del PFD, l'uscita presenta idealmente un'onda quadra di corrente che varia fra tre livelli: ogni fronte di salita del primo segnale ad esempio fa scattare la corrente al livello immediatamente inferiore, mentre ogni fronte del secondo dà luogo ad uno scatto verso il livello superiore. La corrente carica una capacità C, la cui tensione costituisce l'ingresso del VCO. Se i segnali in ingresso sono alla stessa frequenza, l'ingresso del VCO è una rampa (crescente o decrescente a seconda del segno della differenza di fase) intervallata da periodi, di ampiezza proporzionale allo sfasamento dei due segnali, in cui la tensione è costante. Tale ingresso forza il VCO ad annullare lo sfasamento con il segnale di riferimento, raggiungendo la condizione di regime.

Un esempio di PLL a pompa di carica è il CA4046 della RCA

Nel caso invece di due segnali non accordati in frequenza, il VCO riceve in ingresso delle rampe di durata sempre maggiore che lo forzano ad aumentare la frequenza. Tale aumento di frequenza riduce progressivamente la durata delle rampe (in quanto si riduce la differenza di frequenza) e si riesce così a raggiungere la condizione di equilibrio.

- pompa di carica di tipo proporzionale: in questo caso il circuito fornisce carica in proporzione all'errore di fase rilevato dal PFD (a meno di un offset che viene erogato quando i due segnali sono perfettamente in fase). Come nel caso delle pompe di carica bang-bang in parallelo all'ingresso del VCO si trova una capacità C. Il principio di funzionamento è quindi più o meno lo stesso delle push-pull, con la differenza che la corrente di uscita non varia più a livelli ma in proporzione allo sfasamento.

Dead band

[modifica | modifica wikitesto]Una caratteristica dei PLL a pompa di carica è la cosiddetta dead band o dead zone (letteralmente "banda morta"). Si tratta di un intervallo di possibili differenze di fase tra i due segnali in ingresso al PFD che non producono una tensione di correzione all'ingresso del VCO, causando quindi un offset tra il segnale di riferimento del PLL e quello di uscita[42].

Le pompe di carica di tipo bang-bang sono di più semplice realizzazione, però hanno lo svantaggio di avere sempre una dead band. Quando infatti le fasi del segnale di riferimento e di quello retroazionato sono abbastanza vicine, a causa di non-idealità dei componenti la pompa di carica attiva o nessuna o entrambe le correnti in uscita, con effetto complessivo nullo. Ciò causa un significativo jitter sul segnale di uscita del PLL, perché anche a regime l'offset di fase oscilla tra i due valori estremi della dead band senza produrre alcuna correzione.

Per quanto riguarda le pompe di carica di tipo proporzionale, alcune di queste hanno una dead band alcune no. È possibile infatti in questo caso risolvere il problema della dead band tramite alcune tipologie di progetto che producono delle uscite UP e DOWN non nulle anche se la differenza di fase è nulla[43]. Queste uscite sono molto piccole e fanno in modo che la pompa di carica produca impulsi di corrente positivi e negativi uguali anche se il segnale di uscita è agganciato con quello di riferimento, creando così una specie di equilibrio dinamico. Se gli ingressi sono invece leggermente sfasati, l'impulso UP o DOWN sarà un po' più intenso e la PLL può correggere l'offset. Le PLL con questo tipo di sistema di controllo non hanno una dead band e, a parità di altri fattori, hanno un jitter più basso, determinato dalle limitazioni degli altri componenti.

Modello matematico

[modifica | modifica wikitesto]L'uscita della pompa di carica di tipo bang-bang è quindi un treno di impulsi di corrente che caricano il condensatore. È possibile ricavare un modello matematico di prima approssimazione per il PFD e la charge pump considerando un tempo di osservazione molto maggiore del periodo dei segnali in ingresso. In questa maniera si può affermare che la corrente che carica il condensatore è proporzionale alla variabile , dove e sono le fasi dei due segnali in ingresso. Detta come in precedenza questa differenza di fase, si può scrivere nel dominio di Laplace:

dove è l'uscita della pompa di carica, che si comporta quindi come un ulteriore integratore oltre al VCO. Si noti che tale relazione è valida anche per una pompa di carica di tipo proporzionale, solo che in questo caso non è necessario considerare un tempo di osservazione molto maggiore del periodo dei segnali.

Se si vuole ottenere un PLL stabile, è necessario porre in serie alla capacità una resistenza R, in quanto dalla teoria dei controlli automatici si sa che un doppio integratore in retroazione è instabile[N 2]. La funzione di trasferimento del PFD con la pompa di carica diventa quindi:

È possibile a questo punto applicare gli strumenti dei controlli automatici per dimensionare correttamente la corrente , la capacità e la resistenza . Si ottiene la seguente funzione di trasferimento complessiva[44]:

cioè sempre un sistema del secondo ordine con la pulsazione naturale e lo smorzamento pari a:

e con uno zero in .

Se viene usata una pompa di carica di tipo bang-bang, questo tipo di PLL presenta un difetto. La serie della resistenza e della capacità, essendo infatti alimentata dalla pompa di carica con impulsi di corrente, produce sull'ingresso del VCO dei gradini di tensione che possono creare una modulazione indesiderata del VCO. Per risolvere tale problema, spesso viene inserita un'ulteriore capacità in parallelo alla serie che funge da filtro. La scelta del valore di capacità deve essere fatta con cura, per evitare di rendere il PLL instabile[45].

Tracking

[modifica | modifica wikitesto]Il problema del tracking consiste nel determinare quali sono le variazioni della frequenza di ingresso che il PLL riesce a seguire in uscita, cioè qual è la gamma di possibili segnali che il PLL riesce ad agganciare[46]. Tali limitazioni sono dovute in parte alle non idealità e, in alcuni casi, alle caratteristiche intrinseche dei componenti usati per il circuito. Esistono due tipi diversi di tracking, statico e dinamico.

Tracking statico

[modifica | modifica wikitesto]Il tracking statico si riferisce alla capacità da parte del PLL di agganciarsi, entro un range di frequenze più o meno ampio, al segnale di ingresso indipendentemente dalla velocità con cui la frequenza di tale segnale viene variata. Tale proprietà è dovuta in parte alle non idealità del VCO e del comparatore di fase, in parte alle loro caratteristiche intrinseche.

Una prima limitazione in particolare è dovuta alla banda di sintonia (tuning range) del VCO, cioè alla differenza tra la massima e la minima frequenza alla quale esso può oscillare. Ovviamente, il PLL non potrà oscillare a frequenze non comprese nella banda di sintonia del VCO.

Un ulteriore problema è l'impossibilità da parte del comparatore di generare output di valore arbitrario, in quanto la caratteristica dei comparatori di fase è tipicamente non-lineare e per ingressi troppo elevati tende a saturare. A causa di ciò, se la massima uscita del comparatore di fase non consente al VCO di raggiungere il suo picco di frequenza, il PLL avrà una banda di sintonia effettiva inferiore a quella dell'oscillatore controllato.

Per risolvere il secondo di questi problemi (il primo è irrisolvibile, in quanto dipende dalle caratteristiche intrinseche del VCO) è possibile inserire un integratore a valle del comparatore di fase, in modo che l'ingresso al VCO non sia più limitato, dato che l'integrale nel tempo di una quantità limitata può essere illimitato. Tale soluzione viene adottata ad esempio nei PLL a pompa di carica.

Tracking dinamico

[modifica | modifica wikitesto]Tracking dinamico significa che il PLL non riesce ad agganciare un segnale solo nel caso di variazioni dell'ingresso eccessivamente rapide (come ad esempio un gradino di frequenza).

Tale fenomeno è dovuto al fatto che i comparatori di fase danno uscita nulla in media se i due segnali al loro ingresso hanno frequenze diverse (). L'uscita del comparatore conterrà comunque delle componenti armoniche alla frequenza . Se tale frequenza ricade nella banda passante del filtro () allora tale componente armonica raggiungerà il VCO, che dopo un certo tempo aggancerà il segnale di ingresso. Se invece , il segnale di errore non raggiungerà mai il VCO, che non potrà agganciare l'ingresso. indica quindi la massima variazione di frequenza istantanea che il PLL può agganciare.

Per risolvere questo problema, è necessario usare un comparatore di fase e frequenza che dia segnale non nullo anche se le frequenze di ingresso sono diverse. Tale soluzione è adottata nei PLL a pompa di carica, che non risentono infatti del tracking dinamico.

Rumore e jitter

[modifica | modifica wikitesto]Un fattore di merito importante per i PLL è la purezza spettrale, cioè il fatto di avere in uscita una riga spettrale molto precisa alla frequenza di lavoro e contributi trascurabili alle altre frequenze. In realtà, a causa del rumore di fase[47], la riga spettrale in uscita di un PLL non è precisa ma presenta componenti spurie. Tale fenomeno, nel dominio del tempo, causa degli sfasamenti casuali dell'onda rispetto all'uscita ideale in assenza di componenti spurie (jitter). Alcune tecnologie sono in grado di ridurre questo fenomeno. Ad esempio i migliori PLL implementati con circuiti digitali sono quelli realizzati in tecnologia ECL, che però consumano molta potenza. Altre tecnologie a consumi più ridotti, come TTL o CMOS, danno invece risultati peggiori.

Un'altra importante proprietà dei PLL è, come già detto, che la differenza di fase tra il segnale di ingresso e quello di uscita sia vicina allo zero. La differenza media nel tempo tra le fasi tra i due segnali del PLL a regime è detta offset statico di fase o errore di fase a regime. La varianza tra le due fasi è invece detta tracking jitter.

Un ultimo importante fattore di merito è la cosiddetta reiezione del rumore di alimentazione e di substrato. Si vuole infatti che la fase e la frequenza del segnale di uscita del PLL non risentano dei rapidi impulsi di tensione che si vengono a creare sulle linee di alimentazione né del rumore della tensione del substrato su cui il PLL è fabbricato.

Per migliorare le caratteristiche di rumore, come detto in precedenza, è fondamentale una progettazione molto accurata dei singoli componenti e in particolare del filtro. Un ulteriore accorgimento possibile è quello di usare un oscillatore injection locked in cascata al VCO.

Modello matematico per il rumore di fase

[modifica | modifica wikitesto]È possibile applicare le tecniche dei controlli automatici anche per studiare come si trasferisce sul segnale di uscita il rumore di fase dovuto al VCO oppure al riferimento di frequenza in ingresso[48]. Si noti che il rumore di fase non è un rumore di tipo additivo sulla tensione ma si manifesta come una componente aleatoria di fase in eccesso .

Rumore di fase dell'ingresso

[modifica | modifica wikitesto]Si immagini di avere un VCO non rumoroso ma di avere il riferimento di frequenza affetto da componenti spurie, modellabili come rumore di fase. In questo caso il segnale di ingresso potrà essere descritto come:

dove è la componente di rumore di fase dovuta al riferimento di frequenza. Si vuole ora valutare il segnale di uscita (in presenza di un divisore di frequenza di modulo ):

e in particolare il rapporto tra le due quantità e , cioè come il rumore di fase in ingresso viene riportato in uscita. È possibile quindi trasformare le due grandezze con la trasformata di Laplace, ottenendo e . La funzione di trasferimento del rumore di fase dal riferimento all'uscita sarà quindi uguale a quella calcolata in precedenza per i segnali utili del PLL, cioè:

Nel caso di un sistema con una funzione di trasferimento come quella del PLL a pompa di carica precedentemente descritta si ricava:

con e uguali a quelli precedentemente calcolati. Si noti quindi come il rumore di fase del riferimento sia amplificato con un guadagno pari a in una banda circa pari a mentre al di sopra venga attenuato. Questo dimostra come l'uso di divisori con moduli molto elevati sia peggiorativo per le specifiche di rumore.

Rumore di fase del VCO

[modifica | modifica wikitesto]Analogamente a quanto fatto precedentemente si può considerare un riferimento di frequenza non rumoroso e un VCO che produce in uscita una componente spuria (si trascuri in questo caso il divisore di frequenza):

La fase di questo segnale è composta da due contributi. Il primo è che è quello che ci si aspetta nel caso ideale, che è già presente nel modello lineare tempo invariante del PLL precedentemente calcolato. L'altro contributo, , è una fase in eccesso, che quindi può essere modellata tramite un ingresso di rumore che si va a sommare all'uscita di un VCO non rumoroso[N 3]. È possibile ora calcolare la funzione di trasferimento tra questo ingresso e l'uscita:

Sempre nel caso del PLL a pompa di carica si ottiene:

cioè il PLL riduce il rumore di fase del VCO fino a una banda all'incirca pari a , mentre al di sopra viene riportato in uscita senza correzioni. Ciò dimostra l'importanza di mantenere più elevata possibile tale banda, in quanto il VCO tipicamente ha componenti di rumore di fase non trascurabili, avendo un fattore di merito in genere non molto elevato. Tale esigenza si scontra con la necessità di effettuare un filtraggio dell'uscita del PD o del PFD, che spesso presenta componenti indesiderate, che quindi richiederebbe una pulsazione piuttosto bassa.

Direct Digital Synthesis

[modifica | modifica wikitesto]È possibile progettare un circuito completamente digitale per la sintesi di frequenza, ottenendo un risultato simile a quello di un PLL. Questa tecnica è detta Direct Digital Synthesis (DDS)[49].

I sintetizzatori di frequenza digitali utilizzano tre componenti di base[50]: un accumulatore, una memoria a sola lettura (Read Only Memory, ROM) e un convertitore digitale-analogico (Digital-to-Analog Converter, DAC). L'accumulatore ha in ingresso un segnale di comando a una certa frequenza . A ogni periodo di tale segnale l'uscita Φ dell'accumulatore viene incrementata, fino a che non raggiunge la saturazione (buffer overflow). L'andamento di Φ quindi è lineare a tratti, generando una forma d'onda simile a un dente di sega che controlla l'indirizzo di memoria della ROM, che contiene una tabella di corrispondenza nella quale ogni cella di memoria contiene un valore numerico di ampiezza di una sinusoide. Tali valori vengono mandati al convertitore digitale-analogico che crea così in uscita un segnale analogico di ampiezza corrispondente. Si noti come anche in questo caso per variare la frequenza del segnale in uscita sia sufficiente modificare il segnale di ingresso.

Questa tecnica, benché sia di semplice progettazione e permetta di variare la frequenza molto velocemente, presenta problemi maggiori rispetto a un PLL per quanto riguarda il rumore di fase, a causa dell'errore di quantizzazione dovuto all'assenza di un oscillatore vero e proprio. Per questo motivo i circuiti DDS non sono adatti per l'impiego come sintetizzatori ad alta frequenza.

Spesso viene quindi usata una tecnica mista DDS-PLL. Il circuito DDS si usa per creare un segnale sinusoidale a frequenza non molto elevata, ma in grado di seguire variazioni dell'ingresso molto rapide. L'uscita del DDS viene poi miscelata con un segnale ad alta frequenza proveniente da un PLL, ottenendo un segnale a una frequenza pari alla somma di quelle dei due segnali. In questo modo si ottiene una soluzione intermedia tra un PLL puro, a risposta più lenta ma spettralmente più precisa, e un circuito DDS puro, più responsivo ma con un rumore di fase più elevato.

Note

[modifica | modifica wikitesto]- Annotazioni

- ^ Ad esempio, se il comparatore di fase è un mixer analogico, è necessario eliminare la frequenza doppia generata.

- ^ Per verificarlo, è sufficiente tracciare il luogo delle radici.

- ^ Ciò è possibile solo perché nel modello lineare del PLL non si è considerata la tensione come uscita del VCO, ma la fase.

- Fonti

- ^ Best, pp. 5-6.

- ^ a b c d Lee, pp. 438-440.

- ^ de Bellescize

- ^ Riguardo all'utilizzo dei PLL nella televisione (standard americano NTSC), ntsc.

- ^ Riguardo alla storia del PLL, van Roon.

- ^ Grebene

- ^ Il datasheet di tale circuito è ottenibile da ACD4046B CMOS Micropower Phase-Locked Loop.

- ^ Best, pp. 3-4.

- ^ Banerjee, pp. 57-61.

- ^ John G. Webster, The Measurement, Instrumentation and Sensors Handbook, Springer, 1999, pp. 19-15, ISBN 3-540-64830-5.

- ^ Yunfeng Wang et al., Design a 4GHz PLL for wireless receiver, in 7th International Conference on ASIC, ottobre 2007, pp. 315-318, DOI:10.1109/ICASIC.2007.4415630.

- ^ B. Memmler et al., New fast-lock PLL for mobile GSM GPRS applications, in Proceedings of the 26th European Solid-State Circuits Conference, settembre 2000, pp. 468-471.

- ^ Wei Huang et al., PLL performance of DS-CDMA systems in the presence of phase noise,multiuser interference, and additive Gaussian noise, in IEEE Transactions on Communications, vol. 46, n. 11, novembre 1998, pp. 1507-1515, DOI:10.1109/26.729395.

- ^ Banerjee, pp. 10-11.

- ^ Banerjee, p. 62.

- ^ Dally, p. 451.

- ^ Horowitz

- ^ Deok-Soo

- ^ Alan B. Grebene, An Integrated Frequency-Selective AM/FM Demodulator, in IEEE Transactions on Broadcast and Television Receivers, BTR-17, n. 2, maggio 1971, pp. 71-80, DOI:10.1109/TBTR1.1971.299560.

- ^ M. O. Sonnaillon et al., High-Frequency Digital Lock-In Amplifier Using Random Sampling, in IEEE Transactions on Instrumentation and Measurement, vol. 57, n. 3, marzo 2008, pp. 616-621, DOI:10.1109/TIM.2007.911584.

- ^ W. D. Llewellyn et al., A 33mb/s Data Synchronizing Phase-locked-loop Circuit, in 1988 IEEE International Solid-State Circuits Conference, febbraio 1988, DOI:10.1109/ISSCC.1988.663590.

- ^ S. Stetson e R.B. Brown, A complementary GaAs PLL clock multiplier with wide-bandwidth andlow-voltage operation, in 18th Annual Gallium Arsenide Integrated Circuit Symposium, novembre 1996, pp. 317-320, DOI:10.1109/GAAS.1996.567898.

- ^ M.J. Callahan, Integrated DTMF receiver, in IEEE Journal of Solid-State Circuits, vol. 14, n. 1, novembre 1979, pp. 85-90, ISSN 0018-9200.

- ^ Lee, p. 442.

- ^ Razavi, pp. 250-251.

- ^ Best, pp. 16-19.

- ^ Best, p. 20.

- ^ In altri testi, come Lee, p. 456, tale flip-flop è chiamato set-reset (S-R).

- ^ Razavi, pp. 249-250.

- ^ Banerjee, cap. 34.

- ^ Lee, p. 635.

- ^ Razavi, p. 18.

- ^ Banerjee, cap. 5.

- ^ Banerjee, cap. 6.

- ^ Banerjee, cap. 9.

- ^ Lee, pp. 442-444.

- ^ Razavi, pp. 255-256.

- ^ Razavi, pp. 256-258.

- ^ Ad esempio, Tool automatico che calcola i parametri del filtro per un PLL del 3º ordine contiene un tool automatico che calcola i parametri di un PLL del terzo ordine.

- ^ Banerjee, sezione PLL design.

- ^ Gardner

- ^ Banerjee, p. 23.

- ^ Banerjee, p. 328.

- ^ Razavi, pp. 262-265.

- ^ Razavi, p. 265.

- ^ Gardner, cap. 5.

- ^ Banerjee, cap. 14.

- ^ Razavi, pp. 266-268.

- ^ Razavi, pp. 285-289.

- ^ Lee, pp. 523-524.

Bibliografia

[modifica | modifica wikitesto]Pubblicazioni

[modifica | modifica wikitesto]- (FR) Henri de Bellescize, La Réception Synchrone, in L'Onde Électrique, vol. 11, giugno 1932, pp. 230-240.

- (EN) Alan B. Grebene, Camenzind Hans R., Phase Locking As A New Approach For Tuned Integrated Circuits, in ISSCC Digest of Technical Papers, febbraio 1969, pp. 100-101.

- (EN) Floyd M. Gardner, Charge-Pump Phase-Lock Loops, in IEEE Transactions on Communications, vol. 28, n. 11, novembre 1980, pp. 1849-1858, ISSN 0090-6778.

- (EN) Kim Deok-Soo, Deog-Kyoon Jeong, A spread spectrum clock generation PLL with dual-tone modulation profile, in Symposium on VLSI Circuits, giugno 2005, pp. 96-99, DOI:10.1109/VLSIC.2005.1469342.

Libri

[modifica | modifica wikitesto]- Howard M. Berlin, La progettazione dei circuiti phase locked loop, Milano, Gruppo Editoriale Jackson, 1979.

- (EN) Jacob Klapper, John T. Frankle, Phase-Locked and Frequency-Feedback Systems, New York, Academic Press, 1972, ISBN 0-12-410850-4.

- (EN) Floyd M. Gardner, Phaselock Techniques, New York, John Wiley & Sons, 1979, ISBN 0-471-04294-3.

- (EN) Dan H. Wolaver, Phase-Locked Loop Circuit Design, Englewood Cliffs, Prentice Hall, 1991, ISBN 0-13-662743-9.

- (EN) Richard C. Dorf, The Electrical Engineering Handbook, Boca Raton, CRC Press, 1993, ISBN 0-8493-0185-8.

- (EN) Jacob Millman e Arvin Grabel, Microelectronics: Digital and Analog Circuits and Systems, Boca Raton, McGraw Hill Higher Education, 1º ottobre 1988, ISBN 0-07-100596-X.

- (EN) Behzad Razavi, Monolithic Phase-locked Loops and Clock Recovery Circuits: Theory and Design, New York, John Wiley and Sons, 1996, ISBN 0-7803-1149-3.

- (EN) William J. Dally, John W. Poulton, Digital Systems Engineering, Cambridge, Cambridge University Press, 1998, ISBN 0-521-59292-5.

- (EN) William F. Egan, Phase-Lock Basics, New York, John Wiley & Sons, 1998, ISBN 0-471-24261-6.

- (EN) Behzad Razavi, RF Microelectronics, Upper Saddle River, Prentice Hall, 1998, ISBN 0-13-887571-5.

- (EN) William F. Egan, Frequency Synthesis by Phase Lock, New York, John Wiley & Sons, 2000, ISBN 0-471-32104-4.

- (EN) Thomas H. Lee, Design of CMOS Radio-Frequency Integrated Circuits, Cambridge, Cambridge University Press, 2004, ISBN 0-521-83539-9.

- (EN) Roland E. Best, Phase-locked loops: design, simulation, and applications, New York, McGraw-Hill, 2007, ISBN 0-07-149375-1.

Voci correlate

[modifica | modifica wikitesto]- Applicazioni

Altri progetti

[modifica | modifica wikitesto] Wikimedia Commons contiene immagini o altri file sul phase-locked loop

Wikimedia Commons contiene immagini o altri file sul phase-locked loop

Collegamenti esterni

[modifica | modifica wikitesto]- Phase-Locked Loop, in Dizionario delle scienze fisiche, Istituto dell'Enciclopedia Italiana, 1996.

Descrizioni generali

[modifica | modifica wikitesto]- (EN) Tony van Roon, Tutorial sui PLL, su uoguelph.ca. URL consultato il 25 febbraio 2009 (archiviato dall'url originale il 24 febbraio 2009).

- (EN) Dean Banerjee, Manuale su funzionamento, simulazione e progettazione di PLL (PDF), su national.com. URL consultato il 25 febbraio 2009 (archiviato dall'url originale il 20 novembre 2008).

- (EN) AN535: Application Note della Freescale sui PLL (PDF), su e-www.motorola.com. URL consultato il 25 febbraio 2009 (archiviato dall'url originale l'8 aprile 2004).

Esempi di datasheet

[modifica | modifica wikitesto]- (EN) ADF4001 200MHz Clock Generator PLL (PDF), su ee.bilkent.edu.tr. URL consultato il 25 febbraio 2009.

- (EN) ACD4046B CMOS Micropower Phase-Locked Loop (PDF), su datasheetcatalog.org. URL consultato il 25 febbraio 2009.

- (EN) NE567/SE567 Tone Decoder / Phase-Locked Loop (PDF), su nxp.com. URL consultato il 25 febbraio 2009 (archiviato dall'url originale il 12 giugno 2009).

Progettazione

[modifica | modifica wikitesto]- (EN) Riguardo al progetto dei filtri passa-basso per i sintetizzatori di frequenza, su mwrf.com. URL consultato il 25 febbraio 2009 (archiviato dall'url originale il 7 febbraio 2009).

- (EN) Tool automatico che calcola i parametri del filtro per un PLL del 3º ordine, su my.athenet.net. URL consultato il 25 febbraio 2009 (archiviato dall'url originale il 25 febbraio 2009).

- (EN) Stimare il rumore di fase e il jitter dei sintetizzatori di frequenza basati su PLL (PDF), su designers-guide.org. URL consultato il 25 febbraio 2009.

- IDT + Timing solutions, su idt.com.

Applicazioni

[modifica | modifica wikitesto]- (EN) Chris Cadogan, Progetto SETI: sulla ricezione di segnali deboli, su setileague.org. URL consultato il 25 febbraio 2009.

- (EN) Creare un PLL a 2.4 GHz in tecnologia CMOS, con tensione di alimentazione di 1.5 V, standard per applicazioni Bluetooth, su wirelessnetdesignline.com. URL consultato il 25 febbraio 2009 (archiviato dall'url originale il 1º luglio 2010).

- (EN) Descrizione dell'uso dei PLL per la ricezione del segnale NTSC, su sxlist.com. URL consultato il 25 febbraio 2009.

- (EN) Mark Horowitz, Chih-Kong Ken Yang e Stefanos Sidiropoulos, I segnali elettrici ad alta velocità: descrizione e limitazioni (PDF), su www-vlsi.stanford.edu, IEEE Micro, 1º gennaio 1998. URL consultato il 25 febbraio 2009 (archiviato dall'url originale il 21 febbraio 2006).

- (DE) PLL come sintetizzatore di frequenza con potenziometro digitale, su elektronik-kompendium.de. URL consultato il 25 febbraio 2009.

- (ES) Come usare un PLL per controllare un motore elettrico, su ucontrol.com.ar. URL consultato il 25 febbraio 2009 (archiviato dall'url originale l'11 ottobre 2007).

| Controllo di autorità | LCCN (EN) sh85100640 · GND (DE) 4174166-3 · BNF (FR) cb11958008k (data) · J9U (EN, HE) 987007541283705171 |

|---|

French

French Deutsch

Deutsch

![{\displaystyle y(t)=KA_{1}A_{2}\cos {(\omega _{1}t)}\cos {(\omega _{2}t+\varphi )}=K{\frac {A_{1}A_{2}}{2}}\left(\cos {[(\omega _{1}+\omega _{2})t+\varphi ]}+\cos {[(\omega _{1}-\omega _{2})t-\varphi ]}\right)}](https://wikimedia.org/api/rest_v1/media/math/render/svg/6a1ce7c98e2e2c18e63e71cb17055c232dc14672)