Transistor-transistor logic

Transistor-transistor-logic (TTL) はバイポーラトランジスタと抵抗器で構成されるデジタル回路の一種。論理ゲート段(例えばANDゲート)と増幅段のどちらの機能もトランジスタを使って実装しているので、(RTLやDTLとの対比で)このように呼ばれている。

半導体を用いた論理回路の代表的なもののひとつであり、通常+5V単一電源のモノリシック集積回路 (IC) ファミリとして、コンピュータ、産業用制御機械、測定機器、家電製品、シンセサイザーなど様々な用途で使われている。TTLという略称は、TTL互換の論理レベルの意味で使われることもあり、TTL ICとは直接関係ないところでも使われている。例えば電子機器の入出力のラベルなどに表示することがある[1]。

DTLの改良品であり、さまざまなメーカーによってICが製造されているが、1970年代にテキサス・インスツルメンツ社(以下 TI, Texas Instruments)の汎用ロジックICファミリ(7400シリーズ)が広く普及して業界標準となった。標準シリーズから、高速版、低消費電力版、高速・低消費電力版などのバリエーションを広げ、初期のマイクロプロセッサの応用の広がりとともにさらに普及した。しかし、バイポーラトランジスタを使うため、低消費電力化・高集積化・低電圧化には向かず、CMOS技術の発達に伴いデジタルICの主力の座をCMOSに譲った。

歴史

[編集]

1961年、TRWの James L. Buie が「新たに開発する集積回路の設計技術に特に適した」ものとして発明。当初は transistor-coupled transistor logic (TCTL) と名付けられていた[2]。最初に製品化されたTTLのICチップは、1963年にシルヴァニア・エレクトリック・プロダクツ が製造したもので Sylvania Universal High-Level Logic family (SUHL) と名付けられた[3]。シルバニア製の電子部品はフェニックス・ミサイルの制御に使われた[3]。TIが軍用規格(動作を保証する温度範囲が広い)の5400シリーズICを1964年に発売し、民生用規格でパッケージもプラスチックにした7400シリーズICを1966年に発売すると、TTLは電子システム設計で広く使われるようになっていった[4]。

TIの7400ファミリは業界標準となった。モトローラ、AMD、フェアチャイルド、インテル、インターシル、シグネティクス、ムラード、シーメンス、SGS-Thomson、ナショナル セミコンダクター[5][6]といった半導体企業が7400ファミリ互換のICを製造した。単に互換TTL部品を各社が製造しただけではなく、他の回路技術を使った互換部品も製造された。ただしIBMは他とは互換性のないTTL部品を製造し、社内でSystem/38、IBM 4300、IBM 3081といった製品に使用していた[7]。なお、54シリーズと74シリーズの中間的な位置付けの製品として、64シリーズも存在し、数年間は製造されたがその後廃止となっている。

"TTL" という略称はバイポーラ汎用ロジックICのその後の世代にも約20年にわたって使われ続け、速度や消費電力が改善されていった。最近のロジックICファミリ[要出典]である 74AS/ALS(アドバンストショットキー)は1985年に登場した[8]。2008年時点でも、TIは様々な古い技術の汎用ロジックICを供給し続けているが、価格は以前より高くなっている。一般にTTLロジックICは数百個以上のトランジスタを集積していない。チップ当たりに搭載される機能は、数個の論理ゲートからビットスライス式のマイクロプロセッサの範囲である。TTLの重要な特徴はその低価格さであり、そのためにそれまでアナログ回路で実現していた機能が次々とデジタル化されていった[9]。

パーソナルコンピュータの先祖の1つとされる Kenbak-1 はCPUをTTLで構成したもので、1971年当時マイクロプロセッサはまだ入手できなかった[10]。1973年の Xerox Alto と1981年の Star ワークステーションはGUIを導入したことで知られているが、ALUやビットスライス単位のTTLチップを使って構成されていた。1990年代まで、多くのコンピュータはLSIの間をTTL互換ロジックで接続するという形で構成されていた。プログラマブルロジックデバイスなどが登場するまで、TTLに代表されるバイポーラ・ロジックICは開発中のマイクロアーキテクチャのプロトタイピングとエミュレーションに使われていた。

実装

[編集]基本的なTTLゲート

[編集]

TTLはDTL (Diode-transistor logic) を自然に発展させたもので、基本概念は共通である。DTLで入力ダイオードで構成している論理ゲート部分をマルチエミッタ・トランジスタのベース-エミッタ接合を使って実現している。IC上のこの構造は、複数のトランジスタのベースとコレクタをまとめるように接続したのと同等である[11]。単純なTTL論理ゲートの出力はDTLと同様にエミッタ接地回路で増幅される。

全入力にHI電圧 (1) が印加されると、マルチエミッタ・トランジスタのベース-エミッタ接合部に逆バイアスがかかる。このトランジスタは逆方向アクティブモードにあるため(コレクタとエミッタが逆転した状態)、DTLとは対照的に入力から小さい(約10μA)コレクタ電流が流れる。ベース抵抗と供給電圧の組み合わせは実質的に定電流源として機能する[2]。マルチエミッタ・トランジスタのベース-コレクタ接合を通して電流が流れ、出力トランジスタのベース-エミッタ接合がONになる。したがって出力電圧は LO (0) になる。

一方の入力電圧がLO (0) になると、対応するマルチエミッタ・トランジスタのベース-エミッタ接合は2つの直列の接合部(マルチエミッタ・トランジスタのベース-コレクタ接合部と後段のトランジスタのベース-エミッタ接合部)と並列に繋がる。すると入力のベース-エミッタ接合部は出力トランジスタのベース電流を入力ソース(接地)に流れ込ませる[注釈 1]。出力トランジスタのベース電流が遮断されることでスイッチが切れた状態になり[12]、出力電圧はHI (1) になる。遷移の間、入力トランジスタはほぼアクティブ領域にある。そのため出力トランジスタのベース電流の大部分を流れなくし、素早くベースの電位を下げる。TTLがDTLに比べて優れているのは、このようにダイオードを使った入力段よりも高速に遷移する点である[13]。

出力段の単純なTTLの短所は、出力がHI (1) のときの出力抵抗が高く、その値が完全に出力トランジスタのコレクタ抵抗で決まる点である。そのために接続可能な入力数(ファン・アウト)が制限される。単純な出力段の長所として、出力に負荷が接続されていないときに出力の "1" に対応する電圧が高い(VCC に近い)という点が挙げられる。

この種のロジックは出力トランジスタのコレクタ抵抗を省略し、オープンコレクタ出力とすることが多い。そうすると、いくつかの論理ゲートの出力を接続して外部に1つのプルアップ抵抗を用意するという設計が可能となり、ワイヤードANDまたはワイヤードORにすることができる。例えば 7401[14] や 7403 がそのような構成である。

「トーテムポール」出力段のあるTTL

[編集]

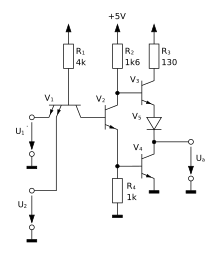

単純な出力段では出力抵抗が高いという問題を解決するには、「トーテムポール」出力(プッシュプル出力)段を追加する。右図のように2つのNPNトランジスタ V3 と V4、ダイオード V5、電流を制限する抵抗器 R3 で構成される。入力がLOのときの電流の制御の考え方がこの構成でも適用されている[注釈 1]。

V2 がオフのとき V4 もオフとなり、V3 がアクティブ状態となってコレクタ接地回路として働き、HI電圧 (1) が出力される。V2 がオンのとき V4 もオンとなり、出力はLO電圧 (0) となる。V2 と V4 のコレクタ-エミッタ接合は、直列の V3 のベース-エミッタ と V5 のアノード-カソード接合をV4 のベース-エミッタ接合と並列接続する。すると V3 のベース電流が流れなくなり、このトランジスタはオフになって出力に影響を与えなくなる。この遷移の際に抵抗器 R3 が直列接続されているトランジスタ V3 とダイオード V5、さらにトランジスタ V4 に流れる電流を制限する。また、出力電圧がHI (1) のときの出力電流も制限し、接地との短絡接続のときの出力電流も制限する。プルアップ抵抗とプルダウン抵抗を出力段から排除することで、消費電力を増大させずにゲートを強化できる[15][16]。

トーテムポール出力段付きTTLの最大の利点は、HI (1) 出力の際の低出力抵抗である。その値はコレクタ接地回路として動作している上段の出力トランジスタ V3 によって決まる。抵抗器 R3 は V3 のコレクタに接続されており、負帰還によってその影響が補償されるため、出力抵抗にはほとんど影響しない。欠点は出力に負荷が接続されていない場合でも出力のHI電圧が低くなる(3.5V以下)という点である。これは、V3 のベース-エミッタ間と V5 のアノード-カソード間で電圧降下があるためである。

インタフェース

[編集]論理レベルを0にするには入力に向かって電流が流れなければいけないため、DTLと同様にTTLは「電流シンク・ロジック」といわれる。入力電圧がLOのとき、TTLの入力ソース電流は前段に流れ込むので、そちらで吸収されなければならない。この電流の最大値は基本的TTLゲートで約1.6mAである[17]。入力ソースは、こうして流れ込む電流が無視できるレベル(0.8V未満)の電圧しか発生しないよう抵抗値を小さく(500Ω未満)する必要がある。推奨されない使い方だが、使わない入力を常に論理値 "1" にしておくためにどこにも接続しないままにしておくことがある。

標準TTL回路の電源電圧は5ボルトである。TTLの入力信号は接地に対して0Vから0.8VのときLOと定義され、2.2Vから5VのときHIと定義される[18](正確な電圧はロジックの種類や温度によっても異なる)。TTLの出力の電圧範囲はそれよりも狭く、0Vから0.4VがLO、2.6Vから5VがHIとなっていて、それぞれ0.4Vのノイズのための余裕がある。TTLの電圧レベルの規格化により、回路基板上に様々なメーカーのTTLチップが混在することが当たり前となった。同じ製品でも製造日が違えば異なるメーカーのTTLチップを使うことがあった。製造後何年も経った回路基板の修理に新たに製造された同型のTTLチップを使うことが可能である。電気的特性が広く統一されていたため、相性などを考慮する必要がなく、理想的な論理デバイスとして扱えた。

TTL論理ゲートの出力をCMOSゲートの入力に使用する場合など、トーテムポール出力段の論理レベル "1" の電圧を VCC に高めるために、出力ピンと VCC の間に外部抵抗器をはさんで接続することがある[19]。ただしこのようにするとトーテムポール型の出力を単純な基本的TTL出力に戻していることになり、大きな出力抵抗が生じる。

パッケージ

[編集]1965年から1990年にかけての多くの集積回路と同様にTTLデバイスはスルーホール実装用にパッケージされた14ピンから24ピンのDIPが一般的だった。エポキシ樹脂製 (PDIP) が一般的だが、セラミック製 (CDIP) もある。大規模なハイブリッドIC向けにパッケージされていないビームリードつきのチップダイスも作られている。軍用や航空宇宙用には表面実装パッケージの一種であるフラットパック (en) でパッケージされている。今ではTTL互換デバイスの多くは表面実装型のパッケージであり、様々な種類がある。

TTLは全ての入力が1つのベース領域上に形成されるマルチエミッタ・トランジスタになっているため、構造的に集積回路に向いている。個別部品でTTL回路を構成しようとするとコストが高くつくが、ICで実装すると逆にコストが下がる。

他の汎用ロジックICファミリとの比較

[編集]TTLデバイスは一般に等価なCMOSデバイスに比べて消費電力が大きいが、CMOSデバイスがクロック周波数を上げると消費電力が大きくなるのに対して、TTLではそれほど増加しない[20]。ECLに比べると消費電力が少なく設計も容易だが、スイッチング性能は低い。性能と経済性を両立させるためにTTLとECLを混在させてシステムを構築することもあったが、両ファミリの間にレベルを変換するデバイスを必要とした。初期のCMOSデバイスは静電気の放電に対してTTLより弱かった。

TTLデバイスの出力構造により、出力インピーダンスがHI状態とLO状態で異なるため、伝送線の駆動には不向きである。そのため、ケーブルなどで信号を送る際には伝送線駆動のための専用デバイスで出力をバッファリングするのが一般的である。ECLは出力インピーダンスが対称的であり、このような欠点がない。

トーテムポール構造の出力段の場合、上下のトランジスタが同時にONになる瞬間が存在し、電源からの電流がかなりのパルスとなって流れる。このパルスがIC間で影響を及ぼしあい、結果としてノイズマージンが低下し性能も低下する。TTLシステムでは1つか2つのICパッケージ毎にバイパスコンデンサを配置するのが一般的で、それによって電流パルスが他のチップの電源電圧を瞬間的に低下させないようにしている。

いくつかの製造業者は、TTL互換の入出力レベルのCMOSロジックICを販売しており、ピン配置などもTTLと合わせていることが多い。例えば74HCTシリーズはCMOSテクノロジーを使い、バイポーラの74シリーズの部品と置換可能である。

派生品

[編集]技術の進歩により、互換性を保ちながらスイッチング速度や消費電力を改良した部品が生まれた。各ベンダーはそれらをショットキーバリアダイオード付きのTTLとして製品化したが、例えばLSファミリなどの回路構成は実際にはDTLに近い[21]。

標準TTLファミリでは、ゲート遅延が10ns、電力消費がゲート当たり10mWで、電力遅延積(PD積)またはスイッチングエネルギーが約100pJである。その派生および後継のファミリとしては次のものがある。

| シリーズ | 型名表示 | 特徴 | 消費電力(mW/Gate) | 遅延 tpd(nsec) |

|---|---|---|---|---|

| 標準TTL | 74 | 1966年に商品化された初期の標準品 | 10 | 10 |

| ローパワーTTL | 74L | 初期の低消費電力品。但しスピードを犠牲にしている。CMOSに取って代わられた。 | 1 | 33 |

| ハイスピードTTL | 74H | スイッチングが速いが、消費電力が大きい。 | 22 | 6 |

| ショットキーTTL | 74S | 入力部にショットキーバリアダイオードを使って電荷蓄積を防ぎ、より高速なスイッチングを可能にした。ただし消費電力がやはり大きい。 | 19 | 3 |

| ローパワーショットキーTTL | 74LS | 1970年代後半~80年代前半の標準TTL。高い抵抗値で消費電力を低減させ、ショットキーダイオードで高速スイッチングを両立させた。PD積は約20pJ。 | 2 | 9.5 |

| FAST | 74F | 1980年代中ごろにフェアチャイルドが発売した高速ショットキーTTL。PD積は約10pJ。 | 4 | 2.5 |

| アドバンストショットキーTTL | 74AS | 1980年代中ごろに出たS-TTLの改良品 | 20 | 1.5 |

| アドバンストLS-TTL | 74ALS | 1980年代中ごろに出たLS-TTLの改良品。PD積は約4pJと最も小さい。 | 1 | 4 |

多くの製造業者が動作温度範囲が民生用のものとより広範囲な軍事用のものを製品化している。54シリーズはMIL規格、74シリーズは一般用の品質保証規格で製造販売される民生用である。例えば、TIの74シリーズは0℃から75℃までとされているが、54シリーズは-55℃から+125℃までとなっている。軍事用や航空宇宙用に特に品質を高めた高信頼部品もある。放射線耐性を高めたものもある。

TTL入出力電圧 (V)

[編集]基準とされる電圧レベル

- Hiレベル入力電圧: 2.0V以上

- Lowレベル入力電圧: 0.8V以下

- Hiレベル出力電圧: 2.4V以上

- Lowレベル出力電圧: 0.4V以下

用途

[編集]VLSIが登場するまで、TTLのICチップを使ってミニコンピュータやメインフレームのプロセッサを構築するのが標準的技法だった。例えば、DECの初期のVAXやデータゼネラルのEclipseがそのような構成である。他にも数値制御の工作機械、プリンター、ビデオディスプレイ端末などで使われている。マイクロプロセッサが広まるとTTLは「グルーロジック」として重要になり、マザーボード上でVLSIで実装された機能ブロック間を繋ぐ役割を担うようになった。

アナログ回路での利用

[編集]元々はデジタル信号を扱うよう設計されているが、TTLのインバータはアナログ増幅器としても使える。出力と入力の間を抵抗器で繋ぐと、負帰還増幅回路として機能する。アナログ信号をデジタルに変換する場合などに使われるが、単にアナログの増幅を行う用途ではTTLインバータを使うことはない[22]。TTLインバータは水晶振動子の信号増幅にも使われる。

脚注

[編集]注釈

[編集]出典

[編集]- ^ Eren, H., 2003.

- ^ a b Buie, J., 1966.

- ^ a b The Computer History Museum, 2007.

- ^ Bo Lojek, History of semiconductor engineering Springer, 2006 ISBN 3540342575,pages 212-215

- ^ Engineering Staff, 1973.

- ^ L.W. Turner,(ed), Electronics Engineer's Reference Book, 4th ed. Newnes-Butterworth, London 1976 ISBN 0-4-080-0168-2

- ^ Pittler, Powers, and Schnabel 1982, 5

- ^ Texas Instruments, 1985

- ^ Lancaster, 1975, preface.

- ^ Klein, 2008.

- ^ Electronic Principles Physics, Models, and Circuits, first edition 1969, Gray and Searle, page 870

- ^ Transistor–Transistor Logic (TTL). siliconfareast.com. 2005. Retrieved 17 September 2008.

- ^ Millman 1979 pg. 147.

- ^ SN7401 datasheet – Texas Instruments

- ^ Transistor–Transistor Logic (TTL), 2005, p. 1.

- ^ Tala, 2006.

- ^ SN7400 datasheet - Texas Instruments

- ^ TTL standard logic level, n.d.

- ^ TTL-to-CMOS Interfacing Techniques

- ^ Paul Horowitz and Winfield Hill, The Art of Electronics 2nd Ed. Cambridge University Press, Cambridge, 1989 ISBN 0-521-37095-7 page 970 ...CMOS devices consume power proportional to ther switching frequency...At their maximum operating frequency they may use more power than equivalent bipolar TTL devices.

- ^ Ayers, n.d.

- ^ Wobschall, 1987, pp. 209-211.

参考文献

[編集]- Ayers, J. UConn EE 215 notes for lecture 4. Harvard University faculty web page. Archive of web page from University of Connecticut. n.d. Retrieved 17 September 2008.

- Buie, J. Coupling Transistor Logic and Other Circuits. (U.S. Patent 3,283,170). 1 November 1966. United States Patent and Trademark Office. 1 November 1966.

- The Computer History Museum. 1963 - Standard Logic Families Introduced. 2007. Retrieved 16 April 2008.

- Engineering Staff. The TTL Data Book for Design Engineers. 1st Ed. Dallas: Texas Instruments. 1973.

- Eren, H. Electronic Portable Instruments: Design and Applications. CRC Press. 2003. ISBN 0-8493-1998-6. Google preview available.

- Fairchild Semiconductor. An Introduction to and Comparison of 74HCT TTL Compatible CMOS Logic (Application Note 368). 1984. (for relative ESD sensitivity of TTL and CMOS.)

- Horowitz, P. and Winfield Hill, W. The Art of Electronics. 2nd Ed. Cambridge University Press. 1989. ISBN 0-521-37095-7

- Klein, E. Kenbak-1. Vintage-Computer.com. 2008.

- Lancaster, D. TTL Cookbook. Indianapolis: Howard W. Sams and Co. 1975. ISBN 0-672-21035-5.

- Millman, J. Microelectronics Digital and Analog Circuits and Systems. New York:McGraw-Hill Book Company. 1979. ISBN 0-07-042327-X

- Pittler, M.S., Powers, D.M., and Schnabel, D.L. System development and technology aspects of the IBM 3081 Processor Complex. IBM Journal of Research and Development. 26 (1982), no. 1:2–11.

- Standard TTL logic levels. n.d. Twisted Pair Software.

- Tala, D. K. Digital Logic Gates Part-V. asic-world.com. 2006.

- Texas Instruments. Advanced Schottky Family. 1985. Retrieved 17 September 2008.

- Transistor-Transistor Logic (TTL). siliconfareast.com. 2005. Retrieved 17 September 2008.

- Wobschall, D. Circuit Design for Electronic Instrumentation: Analog and Digital Devices from Sensor to Display. 2d edition. New York: McGraw Hill 1987. ISBN 0-07-071232-8

関連項目

[編集]外部リンク

[編集]- Texas Instruments logic family application notes

- TTL NAND and AND gates from Lessons In Electric Circuits by Tony Kuphaldt

French

French Deutsch

Deutsch