DDR3 SDRAM – Wikipédia, a enciclopédia livre

Double Data Rate 3 Synchronous Dynamic Random-Access Memory (memória de acesso aleatório dinâmica síncrona com fluxo de dados duplo tipo 3, DDR3 SDRAM) é um tipo de memória de acesso aleatório dinâmica síncrona (SDRAM) com uma interface de alta largura de banda ("taxa de dados dupla") e está em uso desde 2007. É o sucessor de alta velocidade para DDR e DDR2 e predecessor para chips de memória dinâmica de acesso aleatório síncrono (SDRAM) DDR4. DDR3 SDRAM não é nem para a frente nem para trás compatível com qualquer tipo antes de memória de acesso aleatório (RAM) por causa de tensões diferentes de sinalização, clock e outros fatores.

DDR3 é uma especificação de interface DRAM. As matrizes DRAM reais que armazenam os dados são semelhantes aos tipos anteriores, com desempenho semelhante. O principal benefício do DDR3 SDRAM sobre seu predecessor imediato, DDR2 SDRAM, é sua capacidade de transferir dados com o dobro da taxa (oito vezes a velocidade de seus arrays de memória interna), permitindo maior largura de banda ou taxas de pico de dados.

O padrão DDR3 permite capacidade de chips DRAM de até 8 gigabits (Gbit) e até quatro classificações de 64 bits cada para um máximo total de 16 gigabytes (GB) por DIMM DDR3. Por causa de uma limitação de hardware não corrigida até Ivy Bridge-E em 2013, a maioria das CPUs Intel mais antigas suportam apenas chips de até 4 Gbit para DIMMs de 8 GB (os chipsets Core 2 DDR3 da Intel suportam apenas 2 Gbit). Todas as CPUs AMD suportam corretamente a especificação completa para DIMMs DDR3 de 16 GB.[1]

História

[editar | editar código-fonte]Em fevereiro de 2005, a Samsung lançou o primeiro protótipo de chip de memória DDR3. A Samsung desempenhou um papel importante no desenvolvimento e padronização de DDR3.[2][3] Em maio de 2005, Desi Rhoden, presidente do comitê JEDEC, afirmou que o DDR3 estava em desenvolvimento há "cerca de 3 anos".[4]

A DDR3 foi lançada oficialmente em 2007, mas não se esperava que as vendas ultrapassassem a DDR2 até o final de 2009, ou possivelmente no início de 2010, de acordo com o estrategista da Intel, Carlos Weissenberg, falando durante a parte inicial de sua implementação em agosto de 2008.[5] (A mesma escala de tempo para a penetração no mercado foi declarada pela empresa de inteligência de mercado DRAMeXchange um ano antes, em abril de 2007,[6] e por Desi Rhoden em 2005.[4]) A principal força motriz por trás do aumento do uso de DDR3 tem sido novos Processadores Core i7 da Intel e processadores Phenom II da AMD, ambos com controladores de memória interna: o primeiro requer DDR3, o último recomenda. IDC declarou em janeiro de 2009 que as vendas de DDR3 representariam 29% do total de unidades DRAM vendidas em 2009, aumentando para 72% em 2011.[7]

Sucessor

[editar | editar código-fonte]Em setembro de 2012, a JEDEC lançou a especificação final do DDR4.[8] Os principais benefícios do DDR4 em comparação com o DDR3 incluem uma faixa padronizada mais alta de frequências declock e taxas de transferências de dados[9] e voltagem significativamente mais baixa.

Especificação

[editar | editar código-fonte]Visão geral

[editar | editar código-fonte]Em comparação com a memória DDR2, a memória DDR3 usa menos energia. Alguns fabricantes ainda propõem o uso de transistores de "porta dupla" para reduzir o vazamento de corrente.[10]

De acordo com JEDEC,[11]:111 1,575 volts deve ser considerado o máximo absoluto quando a estabilidade da memória é a consideração mais importante, como em servidores ou outros dispositivos de missão crítica. Além disso, o JEDEC afirma que os módulos de memória deve suportar até 1,80 volts[a] antes de incorrer em danos permanentes, embora não sejam necessários para funcionar corretamente nesse nível.[11]:109

Outro benefício é seu buffer de pré-busca, que tem 8 bursts de profundidade. Em contraste, o buffer de pré-busca de DDR2 tem profundidade de 4 rajadas e o buffer de pré-busca de DDR tem profundidade de 2 rajadas. Esta vantagem é uma tecnologia que possibilita a velocidade de transferência de DDR3.

Módulos DDR3 pode transferir dados a uma taxa de 800-2133 MT/s usando ambas as rampas e as bordas de uma 400-1066 MHz I/O clock. Isso é o dobro das taxas de transferência de dados DDR2 (400-1066 MT/s usando um clock de E/S de 200-533MHz) e quatro vezes a taxa de DDR (200-400 MT/s usando um clock de I/O de 100-200 MHz). Gráficos de alto desempenho foram um driver inicial de tais requisitos de largura de banda, onde a transferência de dados de alta largura de banda entre framebuffers é necessária.

Como o hertz é uma medida de ciclos por segundo, e nenhum sinal é executado com mais frequência do que qualquer outra transferência, descrever a taxa de transferência em unidades de MHz é tecnicamente incorreto, embora muito comum. Também é enganoso porque varias temporizações de memória são fornecidas em unidades de ciclo de clock, que são a metade da velocidade das transferências de dados.

O DDR3 usa o mesmo padrão de sinalização elétrica que o DDR e o DDR2, Stub Series Terminated Logic, embora em tempos e tensões diferentes. Especificamente, DDR3 usa SSTL_15.[12]

Em fevereiro de 2005, a Samsung demonstrou o primeiro protótipo de memória DDR3, com capacidade de até 512 Mb e largura de banda de 1.066 Gbps.[2] Produtos sob a forma de placas-mãe apareceram no mercado em junho de 2007[13] baseado em P35 chipset 'Bearlake' da Intel com DIMMs em larguras de banda até DDR3-1600 (PC3-12800).[14] O Intel Core i7, lançado em novembro de 2008, se conecta diretamente à memória ao invés de através de um chipset. Os CPUs Core i7, i5 e i3 inicialmente suportavam apenas DDR3. Os processadores da AMD, do soquete AM3, Phenom II X4, lançados em fevereiro de 2009, foram os primeiros a oferecer suporte a DDR3 (embora ainda suportem DDR2 para compatibilidade com versões anteriores).

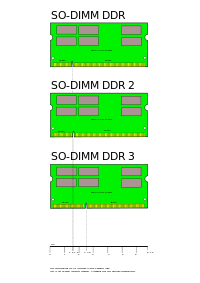

Módulos de memória dual-inline

[editar | editar código-fonte]Os módulos de memória em linha dupla DDR3 (DIMMs) têm 240 pinos e são eletricamente incompatíveis com DDR2. Um entalhe de chave-localizado de forma diferente em DIMMs DDR2 e DDR3 - evita trocá-los acidentalmente. Não apenas eles são chaveados de forma diferente, mas o DDR2 tem entalhes arredondados nas laterais e os módulos DDR3 têm entalhes quadrados nas laterais.[15] DDR3 SO-DIMMs têm 204 pinos.[16]

Para a microarquitetura Skylake, a Intel também projetou um pacote SO-DIMM chamado UniDIMM, que pode usar chips DDR3 ou DDR4. O controlador de memória integrado da CPU pode funcionar com qualquer um deles. O objetivo dos UniDIMMs é lidar com a transição de DDR3 para DDR4, onde o preço e a disponibilidade podem tornar desejável a troca do tipo de RAM. UniDIMMs têm as mesmas dimensões e número de pinos que DDR4 SO-DIMMs regulares, mas o entalhe é colocado de forma diferente para evitar o uso acidental em um soquete DDR4 SO-DIMM incompatível.[17]

Latências

[editar | editar código-fonte]As latências DDR3 são numericamente mais altas porque os ciclos de clock do barramento de E/S pelos quais são medidos são mais curtos; o intervalo de tempo real é semelhante às latências DDR2, em torno de 10 ns. Há algumas melhorias porque o DDR3 geralmente usa processos de fabricação mais recentes, mas isso não é causado diretamente pela mudança para o DDR3.

Latência CAS (ns) = 1000 x CL (ciclos) ÷ frequência do relógio (MHz) = 2000 x CL (ciclos) ÷ taxa de transferência (MT/s)

Enquanto as latências típicas para um dispositivo JEDEC DDR2-800 eram 5-5-5-15 (12,5 ns), algumas latências padrão para dispositivos JEDEC DDR3 incluem 7-7-7-20 para DDR3-1066 (13,125 ns) e 8-8-8-24 para DDR3-1333 (12ns).

Tal como acontece com as gerações anteriores de memória, a memória DDR3 mais rápida tornou-se disponível após o lançamento das versões iniciais. A memória DDR3-2000 com latência 9-9-9-28 (9 ns) estava disponível a tempo de coincidir com o lançamento do Intel Core i7 no final de 2008,[18] enquanto desenvolvimentos posteriores tornaram o DDR3-2400 amplamente disponível (com CL 9-12 ciclos = 7,5-10 ns) e velocidades de até DDR3-3200 disponíveis (com CL 13 ciclos = 8,125 ns).

Consumo de energia

[editar | editar código-fonte]O consumo de energia de chips SDRAM individuais (ou, por extensão, DIMMs) varia com base em muitos fatores, incluindo velocidade, tipo de uso, voltagem, etc. O Power Advisor da Dell calcula que 4 GB ECC DDR1333 RDIMMs usam cerca de 4 W cada.[19] Em contraste, uma parte orientada para desktop mainstream mais moderna de 8 GB, DDR3/1600 DIMM, tem 2,58 W, apesar de ser significativamente mais rápida.[20]

Módulos

[editar | editar código-fonte]| Nome | Chip | Barramento | Timings | ||||||

|---|---|---|---|---|---|---|---|---|---|

| Padrão | Modelo | Módulo | Taxa de clock (MHz) | Tempo de ciclo (ns)[21] | Taxa de clock (MHz) | Taxa de transferência (MT/s) | Largura de barramento (MB/s) | CL-TRCD-TRP | Latência CAS (ns) |

| DDR3-800 | D | PC3-6400 | 100 | 10 | 400 | 800 | 6400 | 5-5-5 | 12.5 |

| E | 6-6-6 | 15 | |||||||

| DDR3-1066 | E | PC3-8500 | 133⅓ | 7.5 | 533⅓ | 1066⅔ | 8533⅓ | 6-6-6 | 11.25 |

| F | 7-7-7 | 13.125 | |||||||

| G | 8-8-8 | 15 | |||||||

| DDR3-1333 | F* | PC3-10600 | 166⅔ | 6 | 666⅔ | 1333⅓ | 10666⅔ | 7-7-7 | 10.5 |

| G | 8-8-8 | 12 | |||||||

| H | 9-9-9 | 13.5 | |||||||

| J* | 10-10-10 | 15 | |||||||

| DDR3-1600 | G* | PC3-12800 | 200 | 5 | 800 | 1600 | 12800 | 8-8-8 | 10 |

| H | 9-9-9 | 11.25 | |||||||

| J | 10-10-10 | 12.5 | |||||||

| K | 11-11-11 | 13.75 | |||||||

| DDR3-1866 | DDR3-1866J* DDR3-1866K DDR3-1866L DDR3-1866M* | PC3-14900 | 233⅓ | 4.286 | 933⅓ | 1866⅔ | 14933⅓ | 10-10-10 11-11-11 12-12-12 13-13-13 | 10.56 11.786 12.857 13.929 |

| DDR3-2133 | DDR3-2133K* DDR3-2133L DDR3-2133M DDR3-2133N* | PC3-17000 | 266⅔ | 3.75 | 1066⅔ | 2133⅓ | 17066⅔ | 11-11-11 12-12-12 13-13-13 14-14-14 | 10.313 11.25; 12.188 13.125; |

* opcional

DDR3-xxx denota taxa de transferência de dados e descreve chips DDR, enquanto PC3-xxxx denota largura de banda teórica (com os dois últimos dígitos truncados) e é usado para descrever DIMMs montados. A largura de banda é calculada tomando transferências por segundo e multiplicando por oito. Isso ocorre porque os módulos de memória DDR3 transferem dados em um barramento de 64 bits de dados e, como um byte compreende 8 bits, isso equivale a 8 bytes de dados por transferência.

Com duas transferências por ciclo de um sinal de clock quádruplo, um módulo DDR3 de 64 bits de largura pode atingir uma taxa de transferência de até 64 vezes a velocidade do clock da memória. Com os dados sendo transferidos 64 bits por vez por módulo de memória, DDR3 SDRAM fornece uma taxa de transferência de (taxa de clock de memória) x 4 (para multiplicador de clock de barramento) x 2 (para taxa de dados) x 64 (número de bits transferidos) / 8 (número de bits em um byte). Portanto, com uma frequência de clock de memória de 100 MHz, DDR3 SDRAM oferece uma taxa de transferência máxima de 6400 MB/s.

A taxa de dados (em MT/s) é o dobro do clock do barramento de E/S (em MHz) devido à taxa dupla de dados da memória DDR. Conforme explicado acima, a largura de banda em MB/s é a taxa de dados multiplicada por oito.

CL - ciclos de clock de latência do CAS, entre o envio de endereço de coluna para a memória e o início dos dados em resposta

tRCD - Ciclos de relógio entre ativação de linha e leituras/gravações

tRP - Ciclos de relógio entre a pré-carga da linha e a ativação

Frequências fracionais são normalmente arredondadas para baixo, mas arredondar para 667 é comum porque o número exato é 666⅔ e arredondado para o número inteiro é mais próximo. Alguns fabricantes também arredondam para uma certa precisão ou arredondam para cima. Por exemplo, a memória PC3-10666 pode ser listada como PC3-10600 ou PC3-10700.[22]

Nota: Todos os itens listados acima são especificados pela JEDEC como JESD79-3F.[11]:157–165 Todas as taxas de dados de RAM entre ou acima dessas especificações listadas não são padronizadas pelo JEDEC - muitas vezes são simplesmente otimizações do fabricante usandos chips de tolerância mais alta ou overvolted. Destas especificações não padronizadas, a velocidade mais alta alcançada relatada foi equivalente a DDR3-2544, em maio de 2010.[23]

Nomenclatura alternativa: Os módulos DDR3 costumam ser incorretamente rotulados com o prefixo PC (em vez de PC3), por razões de marketing, seguido pela taxa de dados. Sob esta convenção, o PC3-10600 é listado como PC1333.[24]

Detecção de presença serial

[editar | editar código-fonte]A memória DDR3 utiliza detecção de presença serial.[25] Detecção de presenta serial (SPD) é uma maneira padronizada de acessar automaticamente informações sobre um módulo de memória de computador, usando uma interface serial. Normalmente é usado durante o autoteste de inicialização para configuração automática de módulos de memória.

Versão 4

[editar | editar código-fonte]A versão 4 do documento DDR3 Seril Presence Detect (SPD) (SPD4_01_02_11) adiciona suporte para DIMMs de redução de carga e também para 16b-SO-DIMMs e 32b-SO-DIMMs.

JEDEC Solid State Technology Association anunciou a publicação da versão 4 do documento DDR3 Serial Presence Detect (SPD) em 1 de setembro de 2011.[26]

Extensão XMP

[editar | editar código-fonte]A Intel Corporation apresentou oficialmente a Especificação eXtreme Memory Profile (XMP) em 23 de março de 2007 para habilitar extensões de desempenho para entusiastas às especificações JEDEC SPD tradicionais para SDRAM DDR3.[27]

Variantes

[editar | editar código-fonte]Além das designações de largura de banda (por exemplo, DDR3-800D) e variantes de capacidade, os módulos podem ser um dos seguintes:

- Memória ECC, que tem uma faixa de bytes de dados extra usada para corrigir erros menores e detectar erros maiores para melhor confiabilidade. Módulos com ECC são identificados por um ECC ou E adicional em sua designação. Por exemplo: "PC3-6400 ECC" ou PC3-8500E.[28]

- Memória registrada ou sem buffer, que melhora a integridade do sinal (e, portanto, potencialmente as taxas de clock e a capacidade física do slot), armazenando eletricamente sinais com um registrador, ao custo de um clock extra de latência aumentada. Esses módulos são identificados por um R adicional em sua designação, por exemplo PC3-6400R.[29]

- A RAM não registrada (também conhecida como "sem buffer") pode ser identificada por um U adicional na designação.[29]

- Módulos totalmente armazenados em buffer, que são designados por F ou FB e não têm a mesma posição de entalhe que outras classes. Módulos totalmente armazenados em buffer não podem ser usados com placas-mãe feitas para módulos registrados, e a posição diferente do entalhe impede fisicamente sua inserção.

- Módulos de carga reduzida, que são designados por LR e são semelhantes à memória registrada/armazenada em buffer, de forma que os módulos LRDIMM armazenem em buffer as linhas de controle e de dados enquanto retêm a natureza paralela de todos os sinais. Como tal, a memória LRDIMM fornece grandes capacidades de memória máximas gerais, enquanto aborda alguns dos problemas de desempenho e consumo de energia da memória FB induzida pela conversão necessária entre as formas de sinal serial e paralelo.

Os tipos de memória FBDIMM (totalmente em buffer) e LRDIMM (carga reduzida) são projetados principalmente para controlar a quantidade de corrente elétrica que flui de e para os chips de memória a qualquer momento. Eles não são compatíveis com a memória registrada/em buffer e as placas-mãe que os exigem geralmente não aceitam nenhum outro tipo de memória.

Extensões DDR3L e DDR3U

[editar | editar código-fonte]O DDR3L (DDR3 Low voltagem) padrão é um adendo ao JESD79-3 DDR3 Memory Device Standard especificando dispositivos de baixa tensão.[30] O padrão DDR3L é 1,35V e possui a etiqueta PC3L para seus módulos. Os exemplos incluem DDR3L-800 (PC3L-6400), DDR3L-1066 (PC3L-8500), DDR3L-1333 (PC3L-10600) e DDR3L-1600 (PC3L-12800). A memória especificada para as especificações DDR3L e DDR3U é compatível com o padrão DDR3 original e pode funcionar na tensão mais baixa ou a 1,50 V.[31] No entanto, os dipositivios que requerem DDR3L explicitamente, que operam a 1,35 V, como sistemas que usam dispositivos móveis as versões dos processadores Intel Core de quarta geração não são compatíveis com a memória 1.50 V DDR3.[32] DDR3L é diferente e incompatível com o padrão de memória móvel LPDDR3.

O padrão DDR3U (DDR3 Ultra Low Voltagem) é de 1,25 V e possui o rótulo PC3U para seus módulos.[33]

JEDEC Solid State Technology Association anunciou a publicação de JEDEC DDR3L em 26 de julho de 2010[34] e DDR3U em outubro de 2011.[35]

Resumo de recursos

[editar | editar código-fonte]Componentes

[editar | editar código-fonte]- Introdução do pino RESET assíncrono

- Suporte de compensação de tempo de voo em nível de sistema

- On-DIMM pinagem DRAM espelho-friendly

- Introdução de CWL (latência de gravação CAS) por caixa de clock

- Motor de calibração de E/S na matriz

- Calibração de Leitura e Escrita

- O recurso ODT dinâmico (On-Die-Termination) permite diferentes valores de terminação para leituras e gravações

Módulos

[editar | editar código-fonte]- Comando/endereço/barramento de controle fly-by com terminação em DIMM

- Resistores de calibração de alta precisão

- Não são compatíveis com verões anteriores - módulos DDR3 não cabem em soquetes DDR2; força-los pode danificar o DIMM e/ou a placa-mãe.[36]

Vantagens tecnológicas sobre DDR2

[editar | editar código-fonte]- Maior desempenho de largura de banda, até 2.133 MT/s padronizado

- Latências ligeiramente melhoradas, medidas em nanossegundos

- Maior desempenho com baixa energia (maior vida útil da bateria em laptops)

- Recursos aprimorados de baixo consumo de energia

Ver também

[editar | editar código-fonte]Notas

- ↑ Antes da revisão F, o padrão afirmava que 1,975 V era a classificação DC máxima absoluta.

Referências

- ↑ Cutress, Ian (11 de fevereiro de 2014). «I'M Intelligent Memory to release 16GB Unregistered DDR3 Modules». anandtech.com. Consultado em 4 de janeiro de 2022

- ↑ a b «Samsung Demonstrates World's First DDR 3 Memory Prototype». Phys.org. 17 de fevereiro de 2005. Consultado em 4 de janeiro de 2022

- ↑ «Our Proud Heritage from 2000 to 2009». Samsung Semiconductor. Samsung. Consultado em 4 de janeiro de 2022

- ↑ a b Sobolev, Vyacheslav (31 de maio de 2005). «JEDEC: Memory standards on the way». DigiTimes.com. Consultado em 4 de janeiro de 2022. Arquivado do original em 13 de abril de 2013.

JEDEC is already well along in the development of the DDR3 standard, and we have been working on it for about three years now.... Following historical models, you could reasonably expect the same three-year transition to a new technology that you have seen for the last several generations of standard memory

- ↑ «IDF: "DDR3 won't catch up with DDR2 during 2009"». pcpro.co.uk. 19 de agosto de 2008. Consultado em 4 de janeiro de 2022. Arquivado do original em 2 de abril de 2009

- ↑ Bryan, Gardiner (17 de abril de 2007). «DDR3 Memory Won't Be Mainstream Until 2009». ExtremeTech.com. Consultado em 4 de janeiro de 2022

- ↑ Salisbury, Andy (20 de janeiro de 2009). «New 50nm Process Will Make DDR3 Faster and Cheaper This Year». MaximumPC.com. Consultado em 4 de janeiro de 2022

- ↑ «JEDEC Announces Publication of DDR4 Standard – JEDEC». JEDEC. Consultado em 4 de janeiro de 2022

- ↑ Shilov, Anton (16 de agosto de 2010). «Next-Generation DDR4 Memory to Reach 4.266GHz – Report». XbitLabs.com. Consultado em 4 de janeiro de 2022. Arquivado do original em 19 de dezembro de 2010

- ↑ McCloskey, Alan. «Research: DDR FAQ». Consultado em 4 de janeiro de 2022. Arquivado do original em 12 de novembro de 2007

- ↑ a b c «DDR3 SDRAM standard (revision F)». JEDEC. Julho de 2012. Consultado em 4 de janeiro de 2022

- ↑ Chang, Jaci (2004). «Design Considerations for the DDR3 Memory Sub-System» (PDF). Jedex. p. 4. Consultado em 4 de janeiro de 2022. Arquivado do original (PDF) em 24 de julho de 2012

- ↑ Soderstrom, Thomas (5 de junho de 2007). «Pipe Dreams: Six P35-DDR3 Motherboards Compared». Tom's Hardware

- ↑ Fink, Wesley (20 de julho de 2007). «Super Talent & TEAM: DDR3-1600 Is Here!». AnandTech

- ↑ DocMemory (21 de fevereiro de 2007). «Memory Module Picture 2007». Consultado em 5 de janeiro de 2022. Cópia arquivada em 6 de junho de 2017

- ↑ «204-Pin DDR3 SDRAM unbuffered SODIMM design specification». JEDEC. Maio 2014. Consultado em 5 de janeiro de 2022

- ↑ «How Intel Plans to Transition Between DDR3 and DDR4 for the Mainstream». techpowerup.com. Consultado em 5 de janeiro de 2022

- ↑ Shilov, Anton (29 de outubro de 2008). «Kingston Rolls Out Industry's First 2GHz Memory Modules for Intel Core i7 Platforms». Xbit Laboratories. Consultado em 5 de janeiro de 2022. Arquivado do original em 1 de novembro de 2008

- ↑ «Dell Energy Smart Solution Advisor». Essa.us.dell.com. Consultado em 5 de janeiro de 2022. Arquivado do original em 1 de agosto de 2013

- ↑ http://www.kingston.com/dataSheets/KVR16N11_8.pdf

- ↑ O tempo de ciclo é o inverso da frequência do clock do barramento de E / S; por exemplo, 1 / (100 MHz) = 10 ns por ciclo de clock.

- ↑ «Pc3 10600 vs. pc3 10666 What's the difference – New-System-Build». Tomshardware.com. Consultado em 5 de janeiro de 2022

- ↑ «Kingston's 2,544 MHz DDR3 On Show at Computex». News.softpedia.com. 31 de maio de 2010. Consultado em 5 de janeiro de 2022

- ↑ «Crucial Value CT2KIT51264BA1339 PC1333 4GB Memory RAM (DDR3, CL9) Retail». www.amazon.co.uk. 10 de maio de 2016. Consultado em 5 de janeiro de 2022

- ↑ «Understanding DDR3 Serial Presence Detect (SPD) Table». simmtester.com. Consultado em 5 de janeiro de 2022

- ↑ «JEDEC Announces Publication of Release 4 of the DDR3 Serial Presence Detect Specification»

- ↑ «Intel Extreme memory Profile (Intel XMP) DDR3 Technology» (PDF). Consultado em 5 de janeiro de 2022. Cópia arquivada (PDF) em 23 de novembro de 2009

- ↑ «Memory technology evolution: an overview of system memory technologies» (PDF). Hewlett-Packard. p. 18. Arquivado do original (PDF) em 24 de julho de 2011

- ↑ a b «What is LR-DIMM, LRDIMM Memory? (Load-Reduce DIMM)». simmtester.com. Consultado em 5 de janeiro de 2022. Cópia arquivada em 20 de outubro de 2014

- ↑ «Addendum No. 1 to JESD79-3 - 1.35 V DDR3L-800, DDR3L-1066, DDR3L-1333, DDR3L-1600, and DDR3L-1866». Maio 2013. Consultado em 5 de janeiro de 2022

- ↑ «Addendum No. 1 to JESD79-3 - 1.35 V DDR3L-800, DDR3L-1066, DDR3L-1333, DDR3L-1600, and DDR3L-1866». Maio 2013. Consultado em 5 de janeiro de 2022.

DDR3L VDD/VDDQ requirements - Power Supply: DDR3L operation = 1.283 V to 1.45 V; DDR3 operation = 1.425 V to 1.575 V .. Once initialized for DDR3L operation, DDR3 operation may only be used if the device is in reset while VDD and VDDQ are changed for DDR3 operation

- ↑ «What is DDR3L Memory?». Dell.com. Dell. 3 de outubro de 2016. Consultado em 5 de janeiro de 2022

- ↑ «Addendum No. 2 to JESD79-3, 1.25 V DDR3U-800, DDR3U-1066, DDR3U-1333, and DDR3U-1600». Outubro 2011. Consultado em 5 de janeiro de 2022

- ↑ «Specification Will Encourage Lower Power Consumption for Countless Consumer Electronics, Networking and Computer Products»

- ↑ «Addendum No. 2 to JESD79-3, 1.25 V DDR3U-800, DDR3U-1066, DDR3U-1333, and DDR3U-1600»

- ↑ «DDR3: Frequently Asked Questions» (PDF). Consultado em 6 de janeiro de 2022. Arquivado do original (PDF) em 29 de dezembro de 2009

Ligações externas

[editar | editar código-fonte]- Padrão JEDEC No. 79-3 (JESD79-3: DDR3 SDRAM)

- DDR3 SDRAM standard JESD79-3F(em inglês)

- Addendum No. 1 to JESD79-3 - 1.35 V DDR3L-800, DDR3L-1066, DDR3L-1333, DDR3L-1600, and DDR3L-1866 (JESD79-3-1A.01)(em inglês)

- Addendum No. 2 to JESD79-3 - 1.25 V DDR3U-800, DDR3U-1066, DDR3U-1333, and DDR3U-1600(em inglês)

- Addendum No. 3 to JESD79-3 - 3D Stacked SDRAM(em inglês)

- SPD (Serial Presence Detect), do padrão JEDEC No. 21-C (JESD21C: configurações JEDEC para memórias de estado sólido)

- DDR, DDR2, DDR3 memory slots testing(em inglês)

- DDR3 Synchronous DRAM Memory(em inglês)

French

French Deutsch

Deutsch