Paritätsbit – Wikipedia

Das Paritätsbit einer Folge von Bits kennzeichnet die Anzahl der mit 1 belegten Bits der Folge, inklusive Paritätsbit, als gerade oder ungerade.

Die „Parität“ der Bitfolge heißt

- gerade (englisch even), wenn die Anzahl der mit 1 belegten Bits in der Folge (inkl. Paritätsbit) gerade ist

- ungerade (englisch odd), wenn die Anzahl der mit 1 belegten Bits in der Folge (inkl. Paritätsbit) ungerade ist.

Das Paritätsbit kann zur Erkennung von Übertragungsfehlern kontrolliert werden. Damit bildet ein Paritätsbit einen binären Blockcode. Die Bitfolge wird in diesem Kontext als Informationswort bezeichnet. Die Paritätskontrollcodierung hängt dem Informationswort ein Paritätskontrollbit, auch Paritybit genannt, an. Das Ergebnis, welches um ein Bit länger ist als das Informationswort, wird hier Codewort genannt.

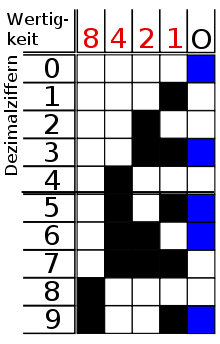

Durch das Anhängen des Paritätsbits haben alle zu übertragenden Codewörter die gleiche Parität(!), vgl. Beispiele in den Grafiken:

- wenn gerade Parität übertragen werden soll, erfolgt die Ergänzung mit E

- wenn ungerade Parität übertragen werden soll, erfolgt die Ergänzung mit O.

Die Methode der Fehlererkennung mittels Paritätsbits heißt Paritätsprüfung. Da nicht bekannt ist, wo innerhalb des Codewortes der Fehler aufgetreten ist, ist keine Fehlerkorrektur möglich. Außerdem ist bei einem Paritätsbit (N = 1) nur eine ungerade Anzahl von Bitfehlern in einem Codewort feststellbar.

Paritätsbits bilden die Grundlage für viele Fehlerkorrekturverfahren wie das unten dargestellte mehrdimensionale Paritätsverfahren, aber auch andere Kanalcodes wie Hamming-Codes und LDPC-Codes.

Berechnung

[Bearbeiten | Quelltext bearbeiten]Versand

[Bearbeiten | Quelltext bearbeiten]Beim Sender wird die Summe der Einsen (Paritätssumme) im Informationswort berechnet. Ist diese Summe gerade, so wird bei Even-Parity das Paritätsbit zu Null; entsprechend ergibt eine ungerade Summe des Informationswortes das Paritätsbit Eins (dies gilt umgekehrt bei Odd-Parity):

| Summe der Einsen eines Informationsworts | Wert des Paritätbits | |

|---|---|---|

| bei Even-Parity | bei Odd-Parity | |

| gerade | 0 | 1 |

| ungerade | 1 | 0 |

Beispiel:

| Informationswort | Summe der Einsen | Paritätsbit / Codewort | |

|---|---|---|---|

| bei Even-Parity | bei Odd-Parity | ||

| 0011.1010 | gerade | 0 / 0011.1010 0 | 1 / 0011.1010 1 |

| 1010.0100 | ungerade | 1 / 1010.0100 1 | 0 / 1010.0100 0 |

Praktisch kann das Paritätsbit sowohl per Hardware als auch per Software erzeugt werden, siehe Paritätsgenerator.

Empfang

[Bearbeiten | Quelltext bearbeiten]Der Empfänger addiert die Bits des empfangenen Codewortes (=Informationswort plus Paritätsbit) ebenfalls und überprüft, ob er denselben Code berechnet hat. Sollte ein Bit verfälscht werden (eine Null in eine Eins oder eine Eins in eine Null), so ist die Paritätssumme des resultierenden Codewortes inkorrekt, und der Dekodierer erkennt, dass es zu einem Fehler gekommen ist. Es ist aber für den Dekodierer nicht möglich, den Fehler zu korrigieren, da nicht bekannt ist, welches Bit verfälscht wurde. Der Dekoder erkennt also maximal einen Fehler und kann maximal null Fehler korrigieren, denn falls mehr als ein Bit verfälscht wurde, so ist es eventuell gar nicht möglich, den Fehler zu erkennen, da die Paritätssumme dann auch gerade sein kann. Man sagt, der Paritätskontrollcode sei 1-fehlererkennend und 0-fehlerkorrigierend.

Anwendungsbereich

[Bearbeiten | Quelltext bearbeiten]Paritätsbits werden u. a. in der DFÜ, Netzwerktechnik und bei Speichermodulen verwendet. Beispielsweise wird die serielle Datenübertragung durch

- 8N1 auf acht Datenbits, ein Stoppbit und ohne (engl. none, „N“) Paritätsbit oder bei

- 7E1 auf sieben Datenbits, ein Stoppbit und gerade (even) Parität

konfiguriert. Für ungerade Parität wird O benutzt.

Die ursprüngliche Form der ASCII-Tabelle besteht aus 128 Zeichen, jedes Zeichen ist durch eine Folge von sieben Bits eindeutig festgelegt. Da ein Rechner acht Bits zu einem Byte zusammenfasst, wurde dieses achte Bit gerne verwendet, um ein Paritätskontrollbit anzuhängen. Heute ist dies jedoch kaum noch üblich, stattdessen wird das achte Bit fast immer zur Erweiterung des Zeichensatzes über 128 Zeichen hinaus verwendet.

Gerade und ungerade Parität

[Bearbeiten | Quelltext bearbeiten]Unterschieden wird zwischen zwei Paritätsprotokollen, in beiden Fällen wird die Anzahl der Einsen innerhalb des zugeordneten Wortes ermittelt:

- Ist die Parität „even“ (gerade) eingestellt, so wird das Paritätsbit gesetzt, falls eine ungerade Anzahl von Einsen im Datenbit im Zeichen gesetzt ist.

- Ist die Parität „odd“ (ungerade) eingestellt, so wird das Paritätsbit gesetzt, falls eine gerade Anzahl von Einsen im Datenbit im Zeichen gesetzt ist.

Mit „gerade“ oder „ungerade“ ist also die Anzahl gesetzter Datenbits inklusive des Paritätsbits gemeint.

Beispiel: Im nachfolgenden Beispiel soll eine ungerade („odd“) Parität hergestellt werden:

| „Wort“ | Paritätsbit | Bemerkungen |

|---|---|---|

| 0100.1110 | 1 | Das „Wort“ enthält bereits vier Einsen, das Paritätsbit wird gesetzt, um ein ungerades Codewort (fünf Einsen) herzustellen. |

| 1011.0110 | 0 | Die Parität ist mit fünf Einsen schon ungerade, das Paritätsbit wird nicht gesetzt. |

| 0100.0000 | 1 | Das gesamte Codewort hat hier zwei Einsen, obwohl die Anzahl ungerade sein sollte. Ein Fehler ist aufgetreten. Entweder wurde das Paritätsbit falsch berechnet, oder das „Wort“ wurde falsch übertragen. |

Bei manchen seriellen Schnittstellen sind außer gerade, ungerade und „kein Paritätsbit verwenden“ noch die beiden Möglichkeiten mark und space verfügbar, wobei mark ein immer gesetztes Paritätsbit darstellt, d. h. unabhängig von der Anzahl gesetzter Datenbits und space ein nie gesetztes Paritätsbit.

Alternative Erklärung

[Bearbeiten | Quelltext bearbeiten]Bei der Übermittlung von Daten in Form eines Bitstroms kann mithilfe von Paritätsbits eine Fehlererkennung stattfinden. Ein Paritätsbit kann dabei eine bestimmte Anzahl von Bits absichern. Der Wert (0 oder 1) des Paritätsbits muss beim Sender berechnet werden und wird beim Empfänger mithilfe der gleichen Berechnung überprüft. Die Berechnung des Paritätsbits kann für gerade oder ungerade Parität erfolgen. Sender und Empfänger müssen vorher definieren/aushandeln, ob sie eine gerade oder ungerade Paritätsberechnung wählen.

Bei Einigung auf die Berechnung einer geraden Parität wird die Anzahl aller 1-Bits in den abzusichernden Daten gezählt. Die Aufgabe des Paritätsbits ist es, diese Anzahl auf eine gerade Anzahl zu erweitern. Wenn die Anzahl der 1-Bits also bereits gerade ist, muss das Paritätsbit als 0 übertragen werden, falls die Anzahl ungerade ist, muss es als 1 übertragen werden.

Bei Einigung auf die Berechnung einer ungeraden Parität wird ebenfalls die Anzahl aller 1-Bits in den abzusichernden Daten gezählt. Die Aufgabe des Paritätsbits ist es, diese Anzahl nun jedoch auf eine ungerade Anzahl zu erweitern. Wenn die Anzahl der 1-Bits also bereits ungerade ist, muss das Paritätsbit als 0 übertragen werden, falls die Anzahl gerade ist, muss es als 1 übertragen werden.

Mehrdimensionale Paritätskontrolle

[Bearbeiten | Quelltext bearbeiten](auch: Kreuzparität oder Blockparität)

Als Erweiterung der oben dargestellten, eindimensionalen Paritätskontrolle lässt sich auch ein zwei- bzw. höherdimensionales Paritätsverfahren erstellen, welches als Erweiterung nicht nur bestimmte Fehler erkennen kann, sondern auch bestimmte Fehlerkombinationen korrigieren kann. Die Paritätskontrolle wird damit zu einem fehlererkennenden und fehlerkorrigierenden Verfahren.

Die Konstruktion soll anhand einer einfachen zweidimensionalen Paritätskontrolle für acht Bit lange Datenwörter dargestellt werden:

- Es werden acht Nutzdatenwörter zu acht Bit Länge (ein Byte) in einem Quadrat (Array) zusammengefasst. Es umfasst somit jede Zeile und jede Spalte genau acht Bit.

- Zu jeder Zeile wird nach dem Verfahren wie oben dargestellt ein Paritätsbit berechnet und als neuntes Datenbit jeder Zeile nachgestellt.

- Zu jeder Spalte wird nach dem Verfahren wie oben dargestellt ein Paritätsbit berechnet und als neunte Zeile angeschrieben.

Das so entstandene Array umfasst neun Mal neun Datenbits und kann geeignet, beispielsweise seriell, übertragen werden. Auf Empfängerseite wird der Datenblock zu neun Datenwörtern empfangen und als Array abgebildet. Tritt nun an einer bestimmten Stelle ein einzelner Bitfehler auf, so ist die Parität genau der betreffenden Zeile und Spalte fehlerhaft. Somit kann das fehlerhafte Bit eindeutig lokalisiert werden und durch Invertierung in den richtigen Zustand umgewandelt werden.

Mit diesem Verfahren sind alle einzelnen Bitfehler pro Block eindeutig erkennbar und korrigierbar. Treten mehrere Bitfehler in einem Block auf, ist die Fehlerkorrektur nicht mehr in allen Fällen möglich. Allerdings sind fehlerhafte Blöcke unter Umständen noch als fehlerhaft erkennbar, was bei diesem Verfahren beispielsweise alle zweifachen Bitfehler pro Block umfasst.

Erweiterte Paritätskontrolle (Blockcodes)

[Bearbeiten | Quelltext bearbeiten]Die Paritätskontrolle wird in erweiterter Form auch bei diversen Blockcodes wie dem Hamming-Code oder dem Low-Density-Parity-Check-Code sowohl zu Fehlererkennung als auch Fehlerkorrektur verwendet. Diese Codes basieren auf einem Nutzdatenblock fixer Länge, an welchem nicht nur ein, sondern mehrere Paritybits angehängt werden, um das eigentliche Codewort zu erzeugen.

Um nicht nur eine Fehlererkennung, sondern auch Fehlerkorrektur mit jenen Paritybits zu ermöglichen, werden in die einzelnen Parity-Bits pro Block unterschiedliche Stellen (Bits) des Nutzdatenblocks eingerechnet. Die Auswahl dieser Stellen pro Paritybit muss nach bestimmten Regeln erfolgen und bestimmte Kriterien wie die lineare Unabhängigkeit der einzelnen Paritystellen gewährleisten, um eine Fehlerkorrektur zu ermöglichen. Aufgrund dieser Codekonstruktionen ergeben sich Möglichkeiten, im Falle von Übertragungsfehlern die genaue Bitposition(en) der Fehler im Nutzdatenblock zu bestimmen und die betroffenen fehlerhaften binären Stellen zu korrigieren.

Eine Erweiterung dieser auf der mehrstelligen Paritätskontrolle basierenden Blockcodes sind die Turbo-Product-Codes (TPC), welche einen erweiterten Parity-Blockcode wie den Hamming-Code mit der oben erwähnten mehrdimensionalen Paritätskontrolle in einer iterativen Dekodierung zwischen Zeilen und Spalten des zweidimensionalen Datenblockes verbinden.

Siehe auch

[Bearbeiten | Quelltext bearbeiten]Literatur

[Bearbeiten | Quelltext bearbeiten]- Ulrich Tietze, Christoph Schenk: Halbleiter-Schaltungstechnik. 12. Auflage. Springer, Berlin u. a. 2002, ISBN 3-540-42849-6.

- Klaus Beuth: Digitaltechnik. 10. überarbeitete und erweiterte Auflage. Vogel, Würzburg 1998, ISBN 3-8023-1755-6 (Elektronik 4; Vogel-Fachbuch).

- Manfred Seifart, Helmut Beikirch: Digitale Schaltungen. 5. völlig neu überarbeitete Auflage. Verlag Technik, Berlin 1998, ISBN 3-341-01198-6.

French

French Deutsch

Deutsch